TCM-32 Magnetic Core Memory Operating and Maintenance Manual

# INSTRUCTION MANUAL MAGNETIC CORE MEMORY SYSTEMS SERIES TCM-32

May 1964

Computer Control Company, Inc.

Old Connecticut Path

Framingham, Massachusetts

COPYRIGHT 1964 by Computer Control Company, Incorporated, Framingham, Massachusetts. Contents of this publication may not be reproduced in any form, in whole or in part, without permission of the copyright owner. All rights reserved.

Printed in U.S.A.

#### TABLE OF CONTENTS

| Paragraph | Title                                                      | Page  |

|-----------|------------------------------------------------------------|-------|

|           | SECTION I<br>INTRODUCTION                                  |       |

| 1-1       | Purpose and Scope of this Manual                           | 1 - 1 |

| 1 - 2     | System Designation                                         | 1 - 1 |

| 1 - 3     | General Description                                        | 1 - 1 |

| 1-4       | Basic Elements and Organization                            | 1 - 2 |

| 1-4.1     | Memory System Layout                                       | 1 - 3 |

| 1-5       | Input Signals                                              | 1-6   |

|           | SECTION II<br>SYSTEM INSTALLATION                          |       |

| 2-1       | General                                                    | 2 - 1 |

| 2-2       | Electrical Interconnections                                | 2-1   |

|           | SECTION III<br>PRINCIPLES OF OPERATION                     |       |

| 3-1       | Principles of Magnetic Core Memories                       | 3-1   |

| 3-1.1     | Magnetic Core Storage                                      | 3 - 1 |

| 3-1.2     | Addressing                                                 | 3-4   |

| 3-1.3     | Information Sensing                                        | 3-6   |

| 3-1.4     | Writing                                                    | 3-7   |

| 3-1.5     | Information Retention                                      | 3-8   |

| 3-2       | General Specifications, TCM-32 Memory System               | 3-8   |

| 3-3       | TCM-32 Functional Description                              | 3-10  |

| 3-3.1     | Address Register                                           | 3-10  |

| 3-3.2     | X- and Y-Decoders, Switches, and Drivers                   | 3-10  |

| 3-3.3     | Memory Timing and Control                                  | 3-12  |

| 3-3.4     | Memory Core Stack                                          | 3-12  |

| 3-3.5     | Information Register                                       | 3-12  |

| 3-3.6     | Sense Amplifiers                                           | 3-12  |

| 3-3.7     | Inhibit Drivers                                            | 3-13  |

| 3-3.8     | Current Drivers                                            | 3-13  |

| 3-4       | Functional Description of Selection and Driving Techniques | 3-13  |

#### TABLE OF CONTENTS (Cont)

| Paragraph | Title                              | Page  |

|-----------|------------------------------------|-------|

| 3-4.1     | Memory Core Stack                  | 3-13  |

| 3-4.2     | Selection Switches                 | 3-15  |

| 3-4.3     | Indicator Option                   | 3-18  |

| 3-5       | Operating Cycles                   | 3-18  |

| 3-5.1     | Standard Cycles                    | 3-18  |

| 3-5.2     | Optional Cycles                    | 3-25  |

| 3-6       | Optional Modes and Features        | 3-26  |

| 3-6.1     | Sequential Addressing              | 3-26  |

| 3-6.2     | Random-Sequential Addressing       | 3-26  |

| 3-6.3     | Sequential-Interlace Addressing    | 3-26  |

| 3-6.4     | Serial Addressing                  | 3-28  |

| 3-6.5     | Serial-Information Inputs          | 3-28  |

| 3-6.6     | Memory Clear                       | 3-28  |

| 3-6.7     | Partial Substitution               | 3-28  |

| 3-6.8     | Signal Compatibility               | 3-29  |

| 3-6.9     | Indicators                         | 3-29  |

|           | SECTION IV<br>LOGIC                |       |

| 4-1       | Logic Diagrams                     | 4-1   |

| 4-2       | Input/Output Logic Signals         | 4-1   |

|           | SECTION V<br>MAINTENANCE           |       |

| 5-1       | General                            | 5-1   |

| 5-2       | Test Equipment                     | 5 - 1 |

| 5-3       | PAC Locations                      | 5 - 1 |

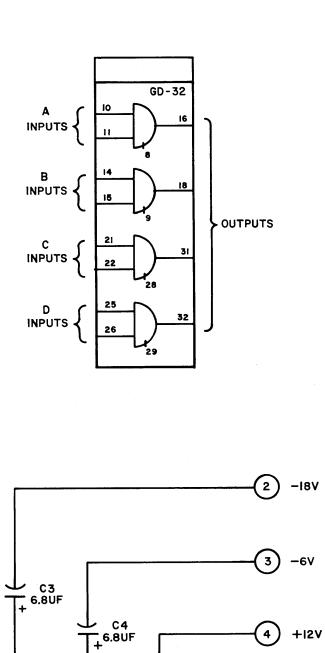

| 5-4       | PAC Handling and Repair Procedures | 5-2   |

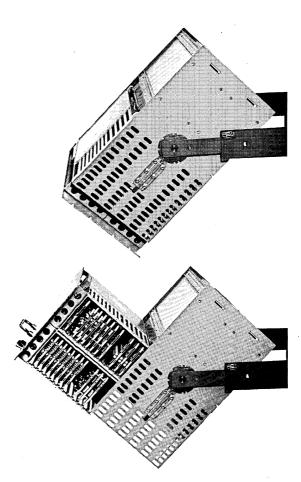

| 5-4.1     | Inserting and Removing System PACs | 5-2   |

| 5-4.2     | PAC Troubleshooting                | 5-2   |

| 5-4.3     | Component Checking                 | 5-2   |

| 5-4.4     | Component Replacement              | 5-3   |

| 5-5       | Spare Parts                        | 5-4   |

| 5-6       | Maintenance Inspection             | 5-4   |

| 5_7       | Proventivo Maintonanao Proceduro   | E E   |

# TABLE OF CONTENTS (Cont)

|   | <u> </u> | Title                             | Page |

|---|----------|-----------------------------------|------|

|   | 5-8      | Corrective Maintenance Procedure  | 5-7  |

| 1 | 5-9      | Magnetic Core Matrix Maintenance  | 5-11 |

| , | 5-10     | Logic Circuit Maintenance         | 5-14 |

|   | 5-11     | DC Power Distribution             | 5-14 |

|   |          | SECTION VI<br>PAC COMPLEMENT LIST |      |

|   | 6-1      | General                           | 6-1  |

# LIST OF ILLUSTRATIONS

| Figure | Title                                                                                                       | Page  |

|--------|-------------------------------------------------------------------------------------------------------------|-------|

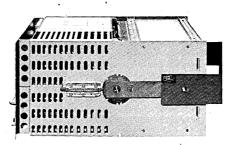

| 1-1    | TCM-32 Magnetic Core Memory System                                                                          | 1-0   |

| 1 - 2  | Memory System, Block Diagram                                                                                | 1-4   |

| 1-3    | Memory System Layout                                                                                        | 1 - 5 |

| 2-1    | Installation Drawing (Sheet 1 of 2)                                                                         | 2-3   |

| 2-1    | Installation Drawing (Sheet 2 of 2)                                                                         | 2-5   |

| 2-2    | Connector Detail                                                                                            | 2-7   |

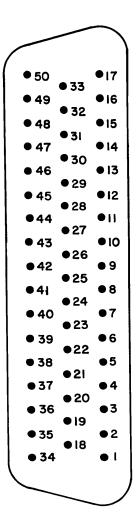

| 2-3    | Pin Numbering, Connectors J-102 through J-107                                                               | 2-8   |

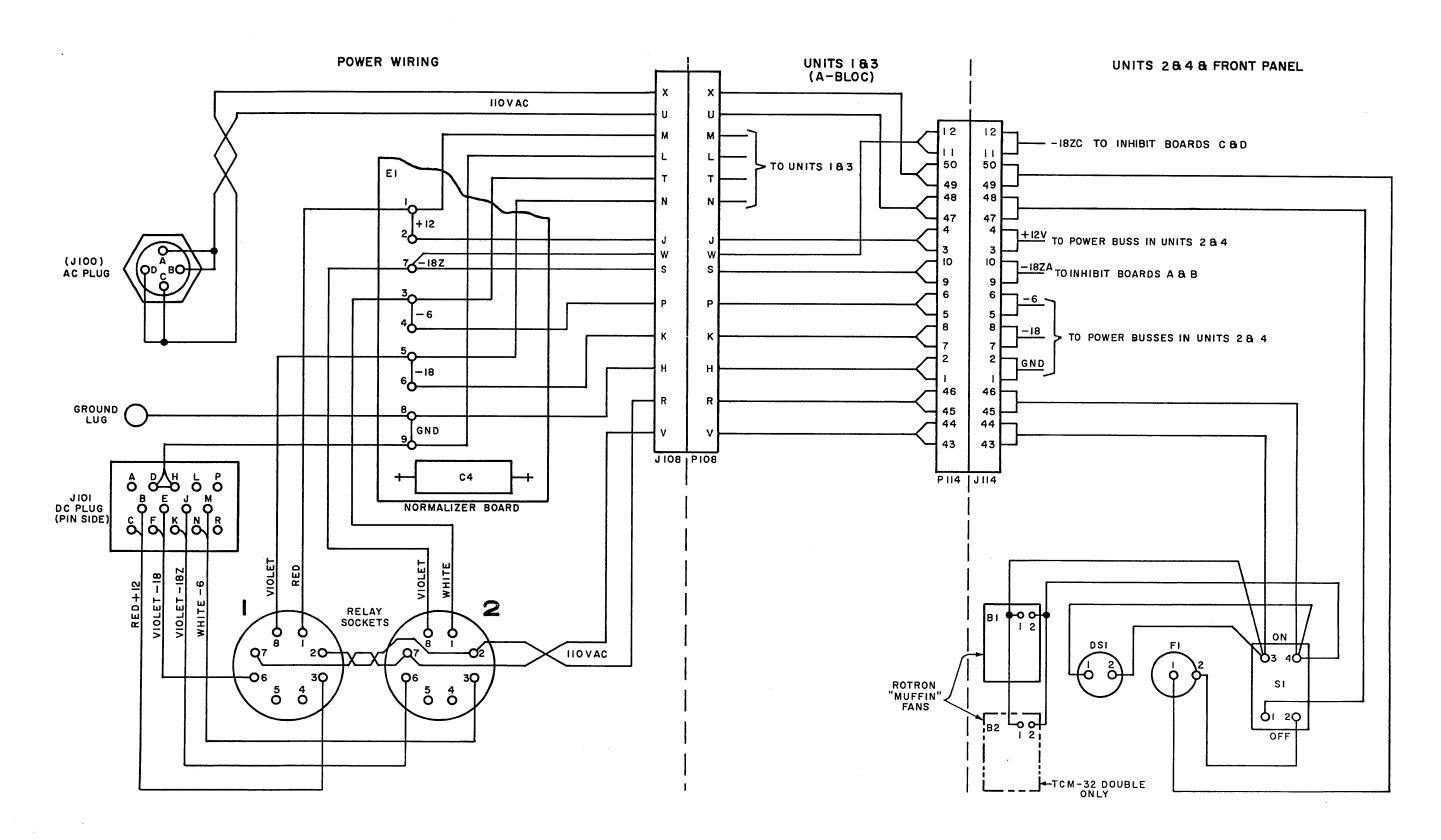

| 2-4    | TCM-32 Power Wiring Diagram                                                                                 | 2-9   |

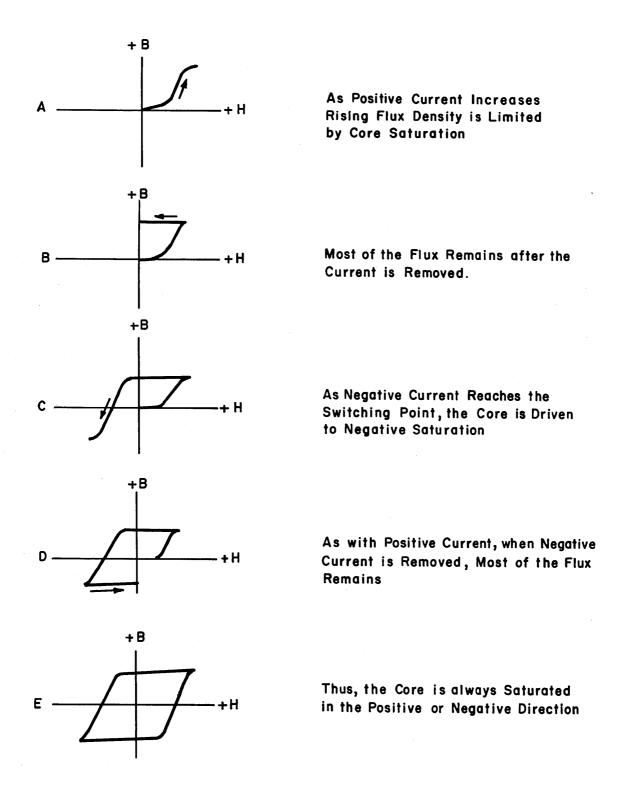

| 3-1    | Ferrite Core Hysteresis Loop                                                                                | 3-2   |

| 3-2    | Core Control Windings                                                                                       | 3-4   |

| 3-3    | Coincident-Current Selection                                                                                | 3-6   |

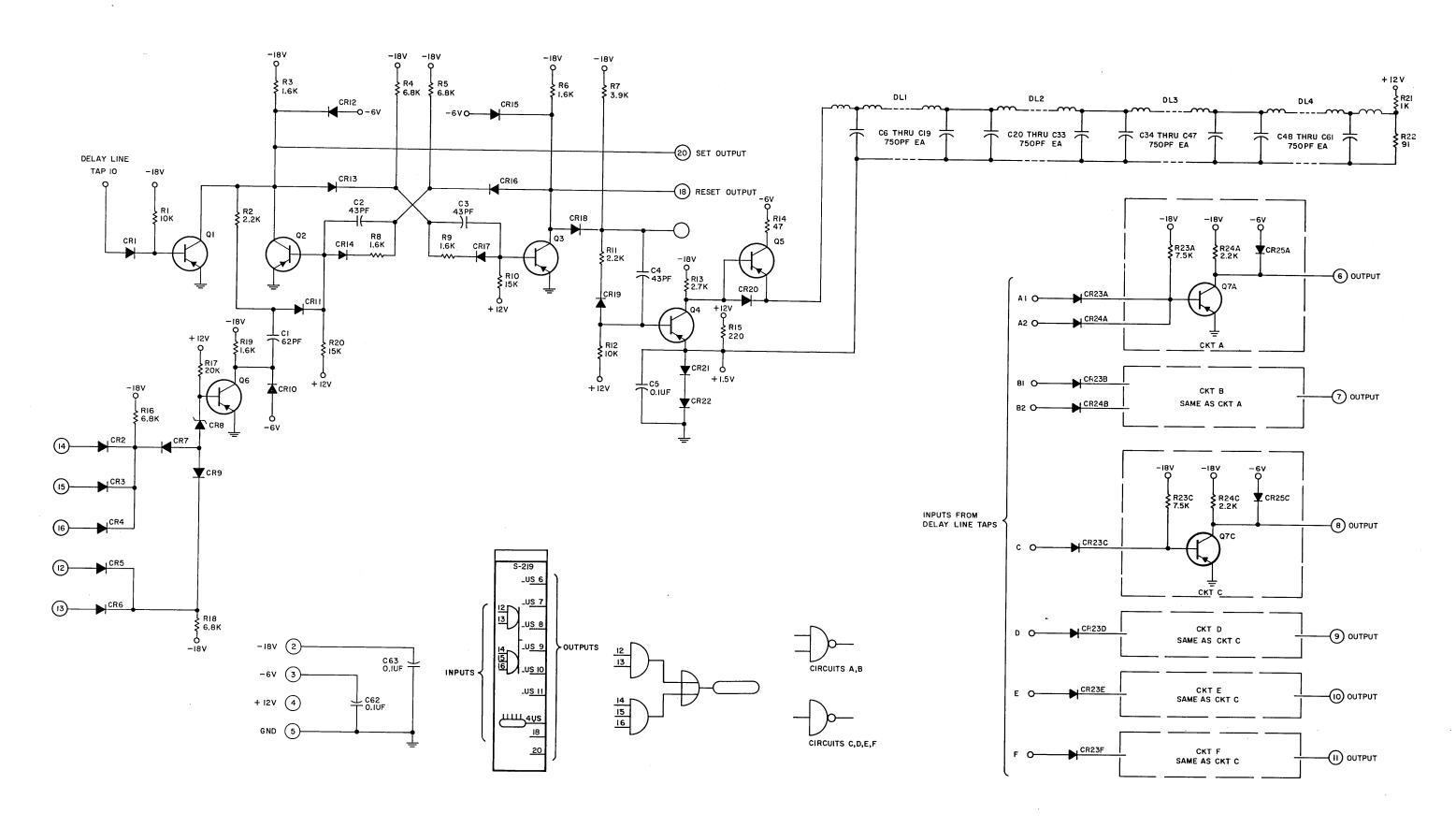

| 3-4    | TCM-32 Memory System, Block Diagram                                                                         | 3-11  |

| 3-5    | Memory Core Stack, Simplified Schematic Diagram of Y-Coordinate Sense, and Inhibit                          | 3-14  |

| 3-6    | Simplified Selection Diagram                                                                                | 3-16  |

| 3-7    | Internal Timing                                                                                             | 3-17  |

| 3-8    | Read/Regenerate Cycle External Timing                                                                       | 3-19  |

| 3-9    | Clear/Write Cycle External Timing                                                                           | 3-20  |

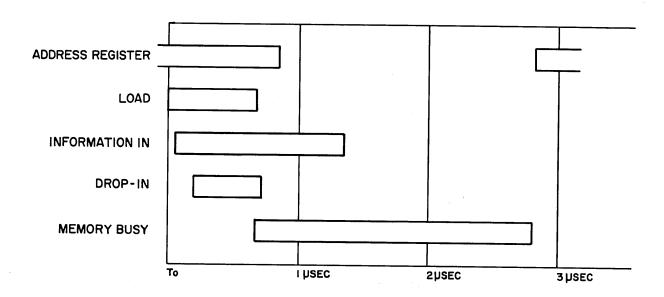

| 3-10   | Load Cycle External Timing                                                                                  | 3-22  |

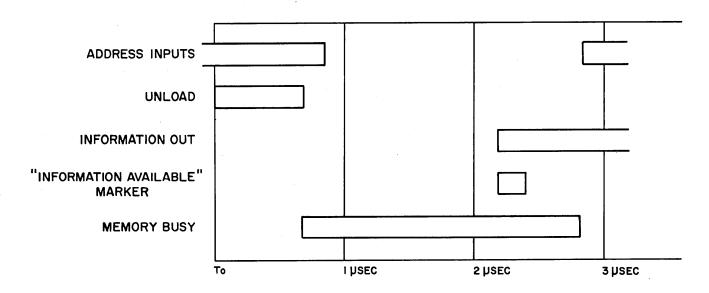

| 3-11   | Unload Cycle External Timing                                                                                | 3-23  |

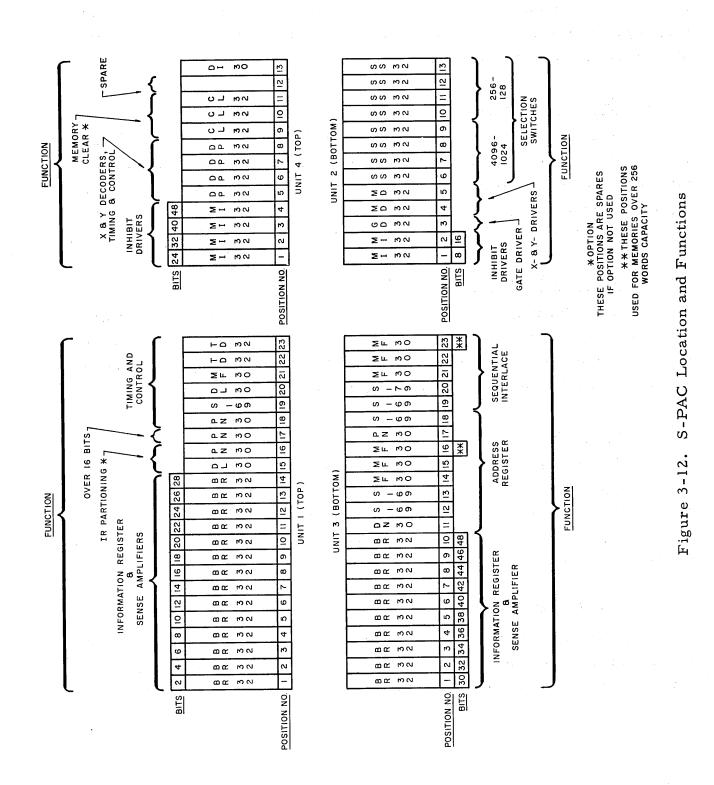

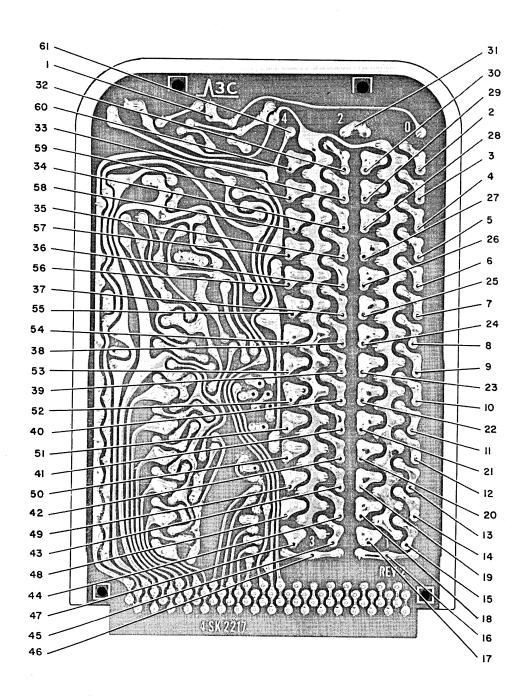

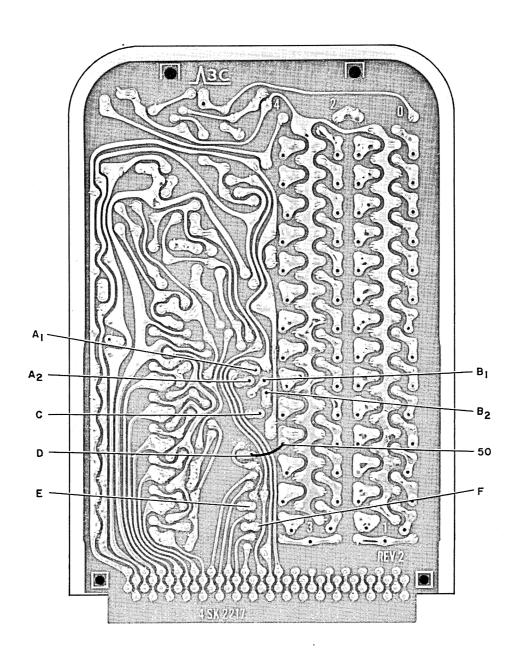

| 3-12   | S-PAC Location and Functions                                                                                | 3-27  |

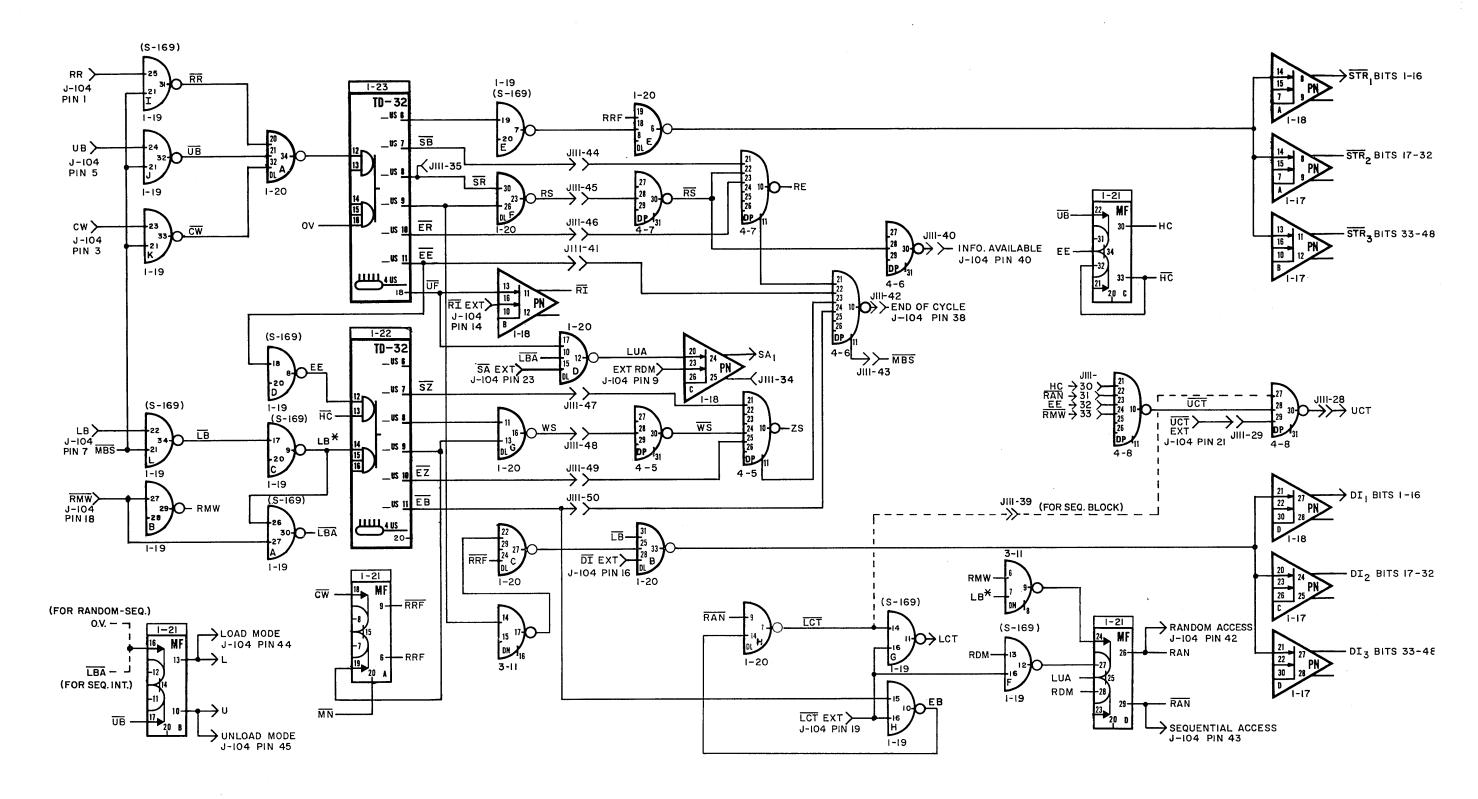

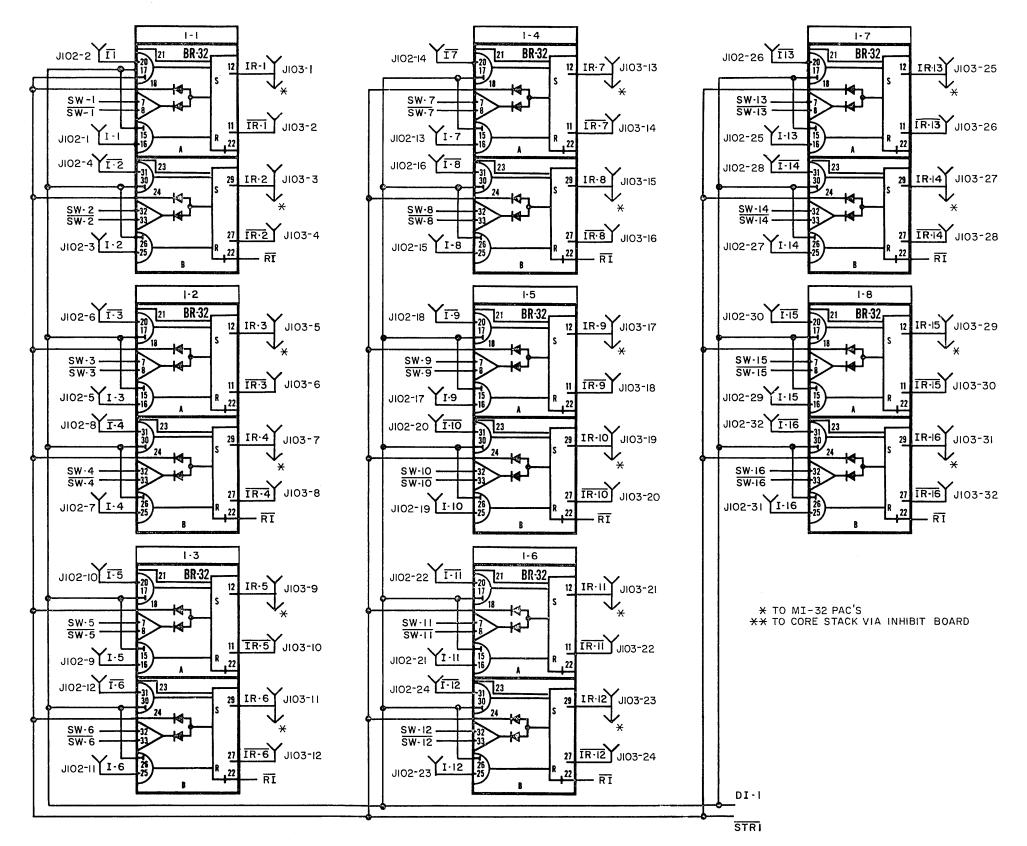

| 4-1    | Memory Timing and Control, Logic Diagram                                                                    | 4-5   |

| 4-2    | Address Register, Logic Diagram (Random Addressing, Sequential Addressing and Random-Sequential Addressing) | 4-7   |

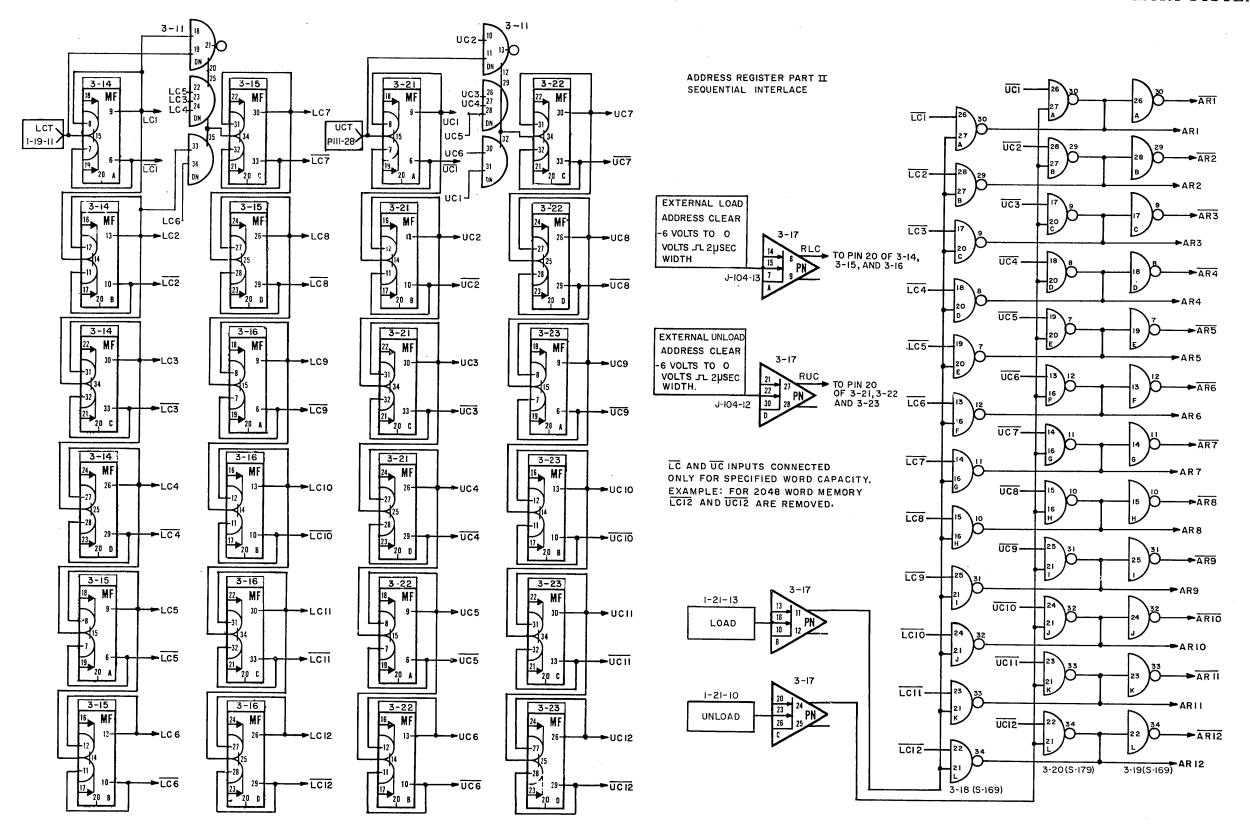

| 4-3    | Address Register, Logic Diagram (Sequential-Interlace Addressing Option)                                    | 4-9   |

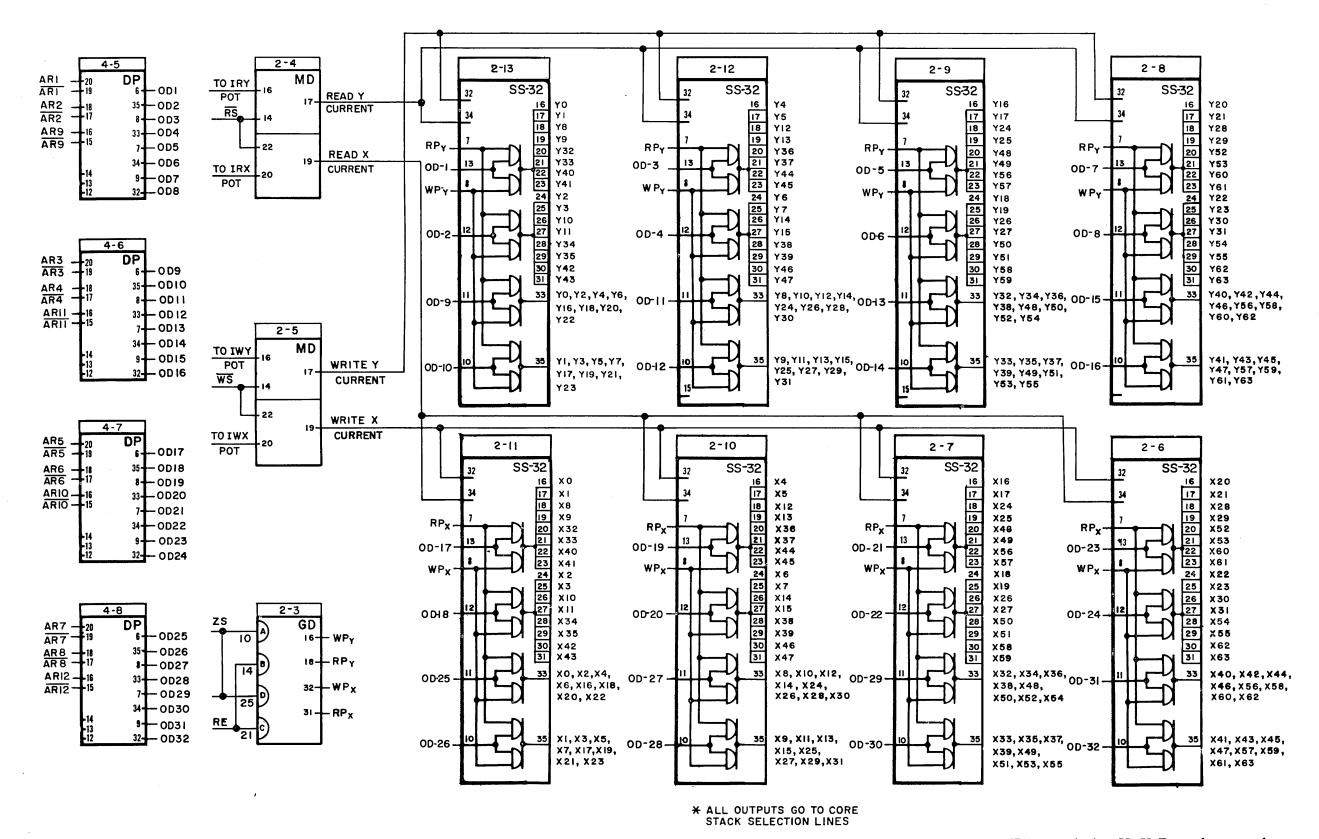

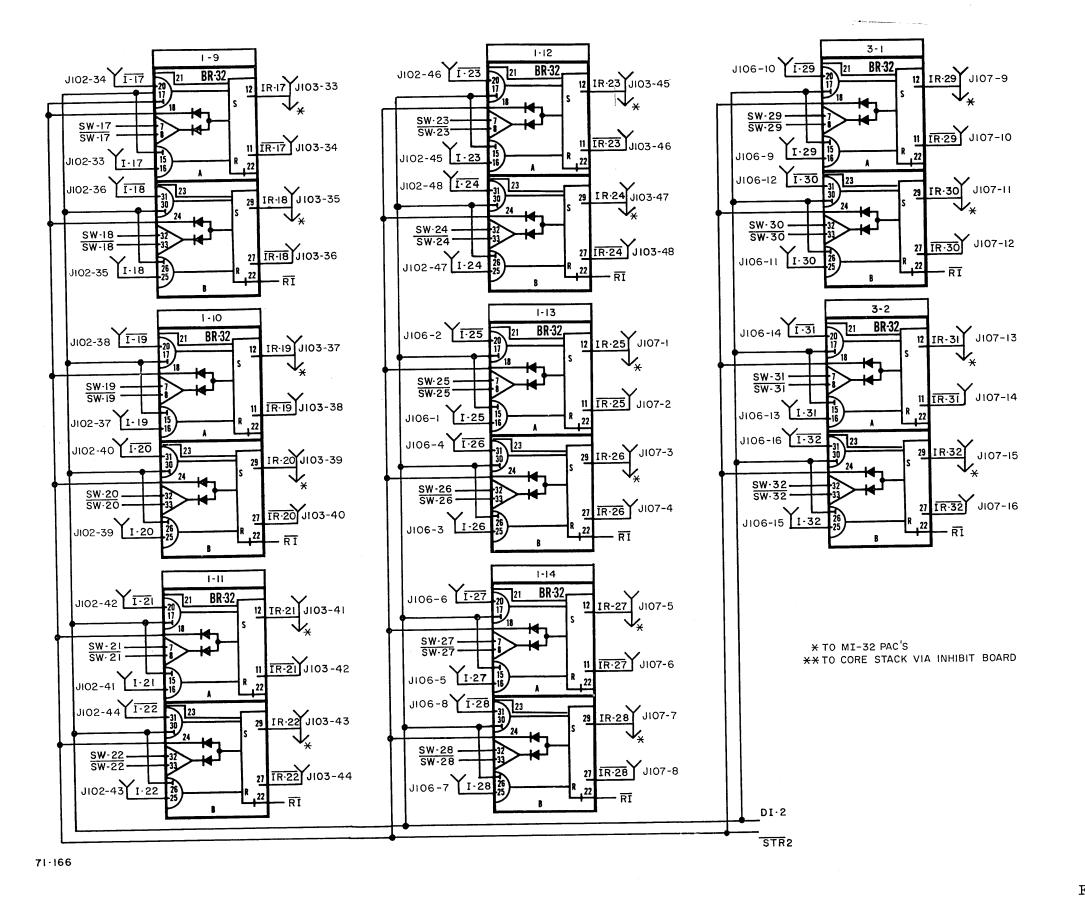

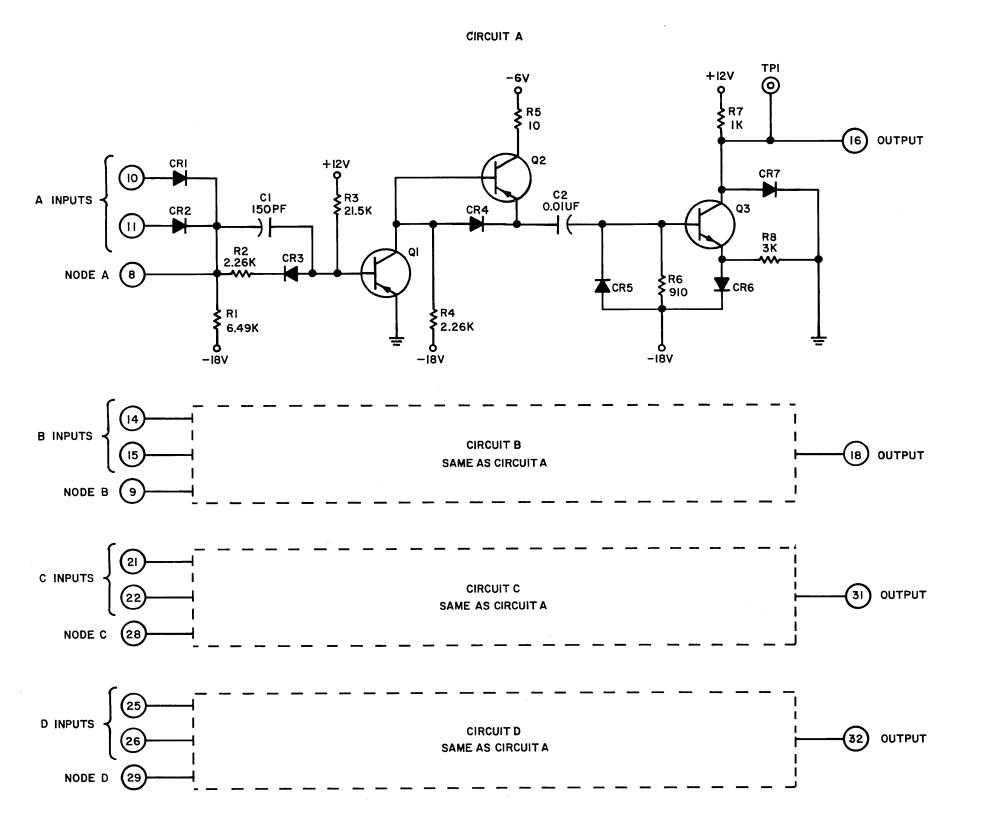

| 4-4    | X-Y Decoders and Selection Switches, Logic Diagram                                                          | 4-11  |

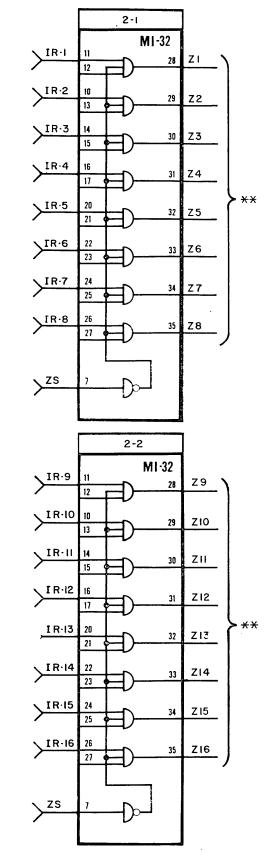

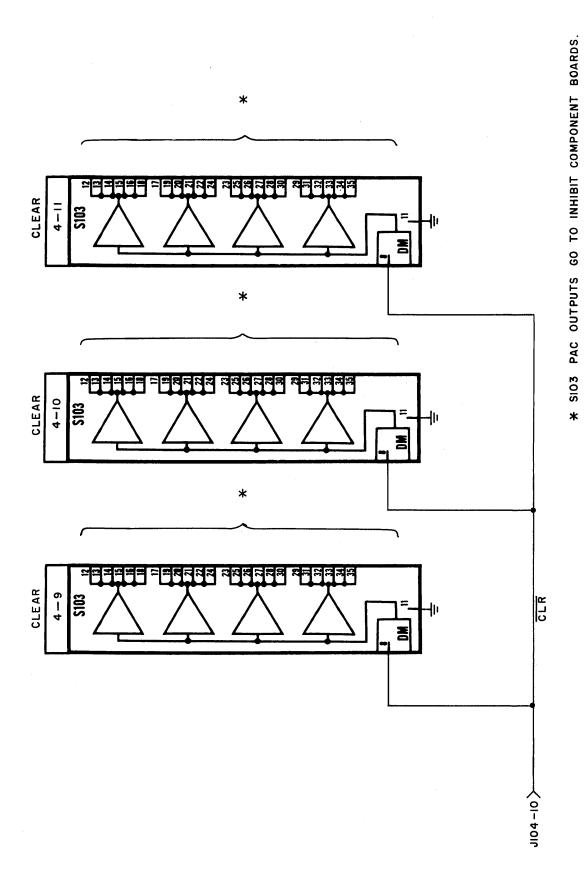

| 4-5    | Information Register, Sense Amplifiers, and Inhibit Drivers, Logic Diagram (Bits 1 through 16)              | 4-13  |

| 4-6    | Information Register, Sense Amplifiers, and Inhibit Drivers, Logic Diagram (Bits 17 through 32)             | 4-15  |

| 4-7    | Information Register, Sense Amplifiers, and Inhibit<br>Drivers, Logic Diagram (Bits 33 through 48)          | 4-17  |

## LIST OF ILLUSTRATIONS (Cont)

| Figure | Title                                                                                                             |              |  |

|--------|-------------------------------------------------------------------------------------------------------------------|--------------|--|

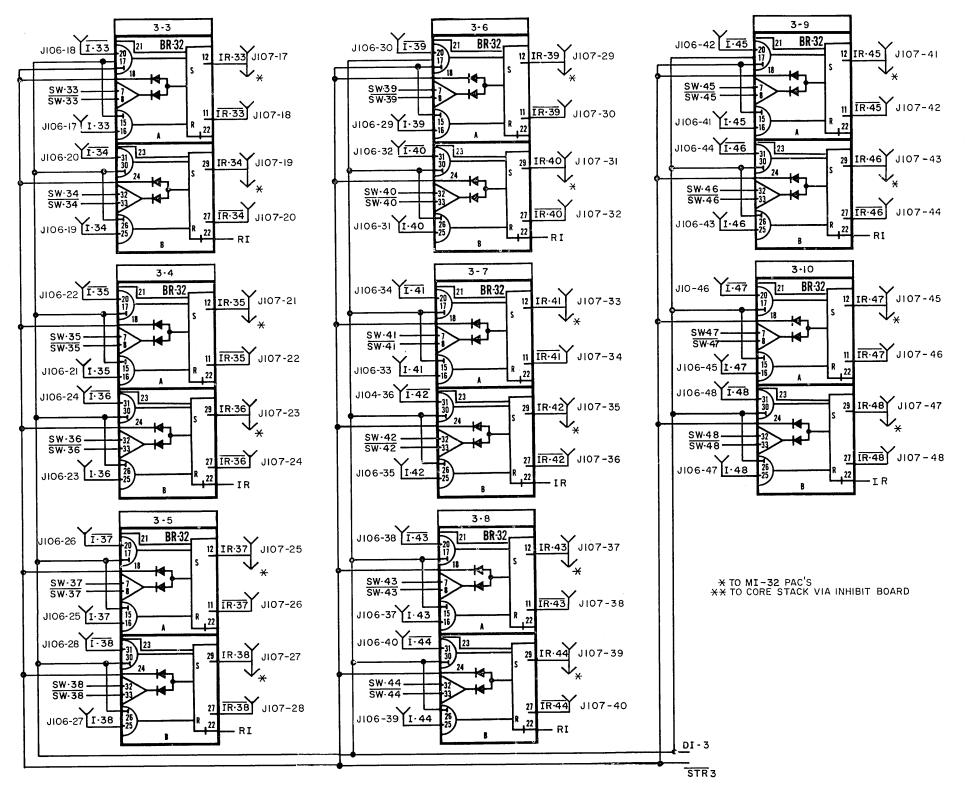

| 4-8    | Partial Substitution Option, Logic Diagram (Two-Zone, Three-Zone, or Four-Zone Information-Register Partitioning) | 4-19         |  |

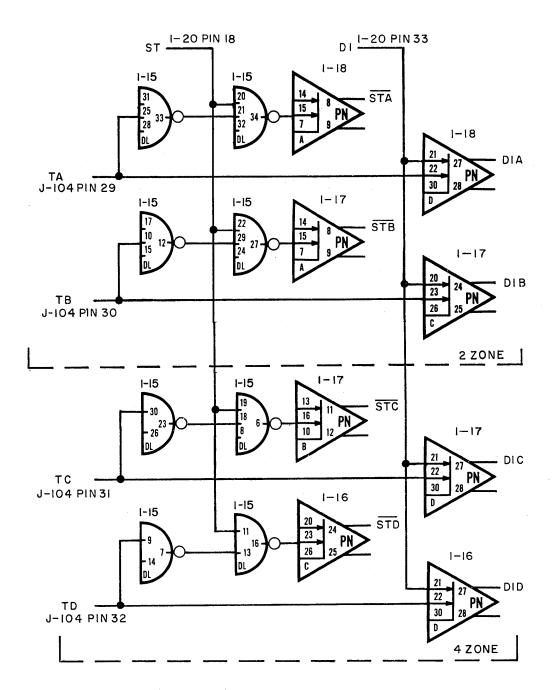

| 4-9    | Clear Option, Logic Diagram                                                                                       | 4-20         |  |

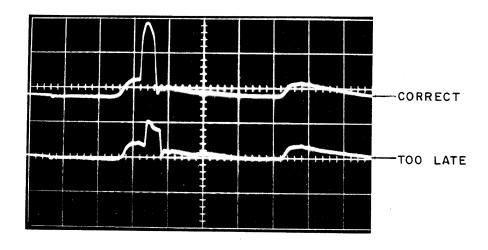

| 5-1    | Strobe Adjustment Waveform                                                                                        | 5-6          |  |

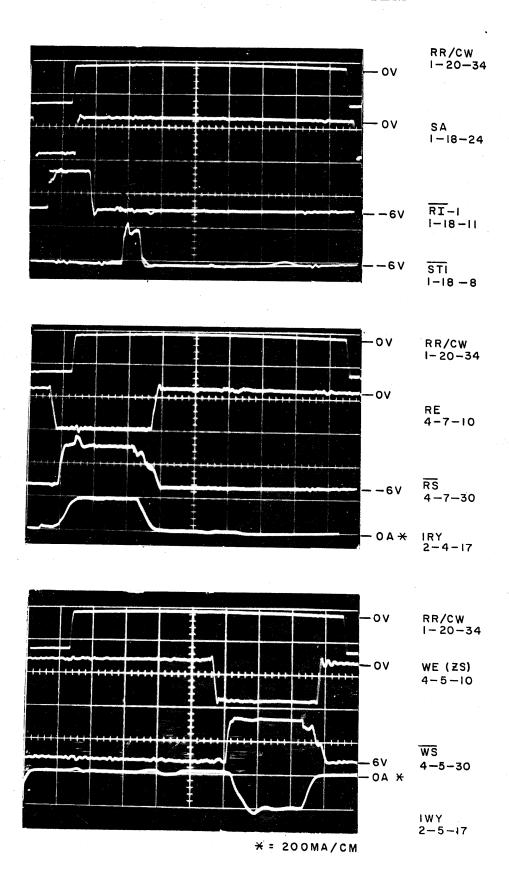

| 5-2    | Waveform (Sheet 1 of 3)                                                                                           | 5-8          |  |

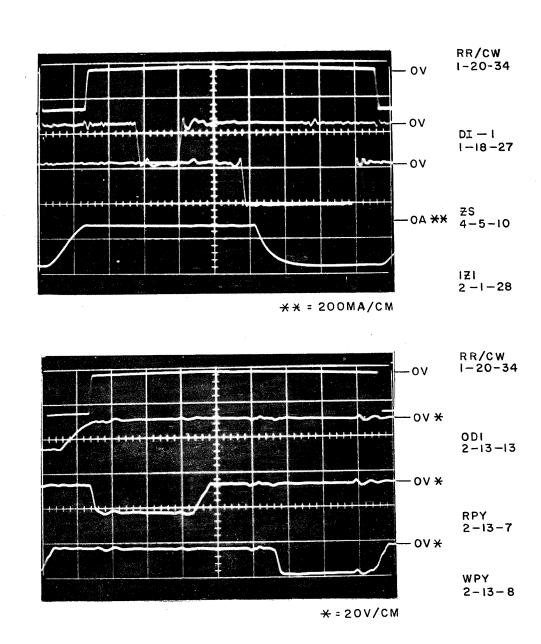

| 5-2    | Waveform (Sheet 2 of 3)                                                                                           | 5 <b>-</b> 9 |  |

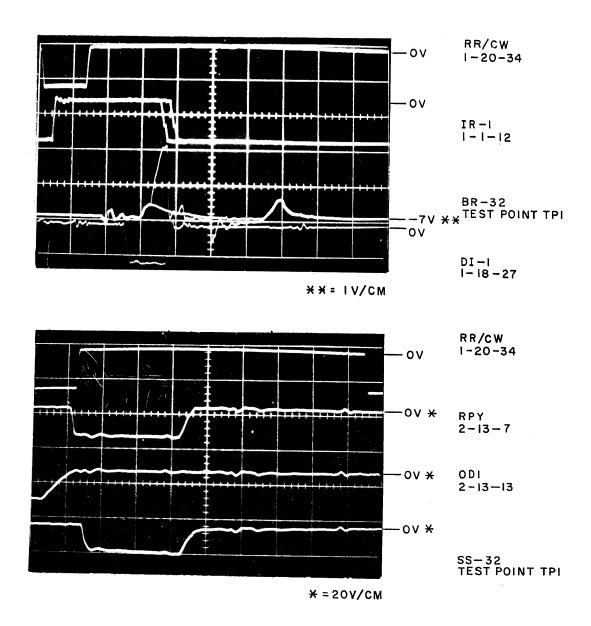

| 5-2    | Waveform (Sheet 3 of 3)                                                                                           | 5-10         |  |

#### LIST OF TABLES

| <u>Table</u> | <u>Title</u>                              | Page |

|--------------|-------------------------------------------|------|

| 2-1          | Wiring Connector J-102                    | 2-11 |

| 2-2          | Wiring Connector J-103                    | 2-12 |

| 2-3          | Wiring Connector J-104                    | 2-13 |

| 2-4          | Wiring Connector J-105                    | 2-15 |

| 2-5          | Wiring Connector, J-106 and J-107         | 2-16 |

| 3-1          | Internal Logic Signals                    | 3-24 |

| 4-1          | Logic Signal List                         | 4-2  |

| 5-1          | Test Equipment Required                   | 5-1  |

| 5-2          | Spare Parts List                          | 5-4  |

| 5-3          | Operation Failures                        | 5-12 |

| 5-4          | Partial Information Word Failures         | 5-15 |

| 5-5          | Address, Decoding, and Selection Failures | 5-17 |

| 5-6          | Inhibit Winding Checklist                 | 5-18 |

| 5-7          | Sense Winding Checklist                   | 5-19 |

| 5-8          | Intra-Unit Wiring Connector               | 5-21 |

| 5-9          | X-Winding Checklist                       | 5-25 |

| 5-10         | Y-Winding Checklist                       | 5-26 |

| 4 1          | PAC Complement List                       | 6-2  |

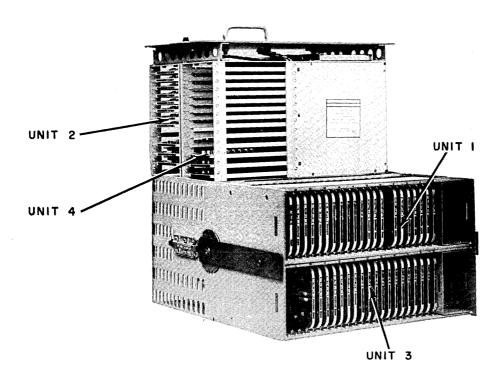

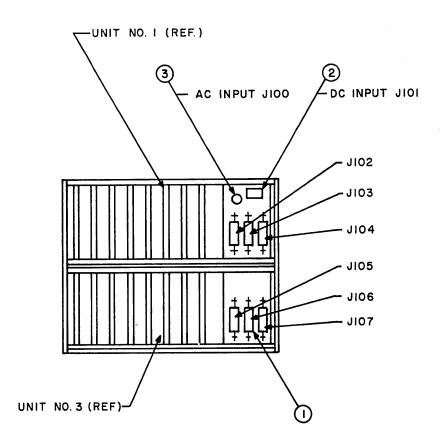

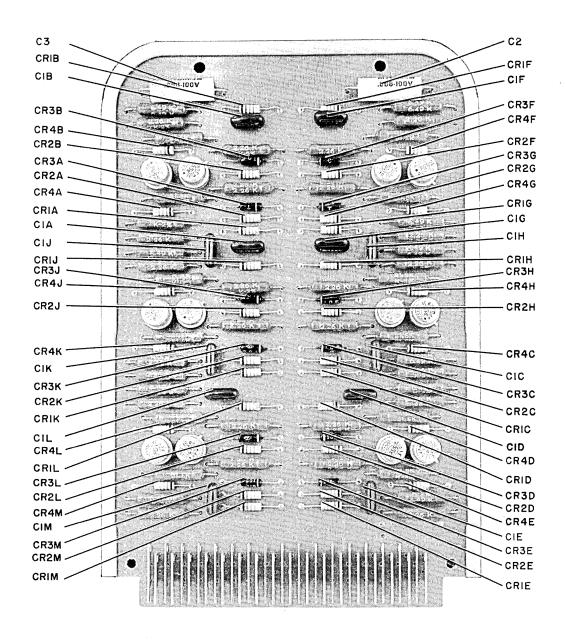

Figure 1-1. TCM-32 Magnetic Core Memory System

# SECTION I INTRODUCTION

#### 1-1 PURPOSE AND SCOPE OF THIS MANUAL

This manual contains information on the theory of operation and instructions for the installation, operation, and maintenance of Series TCM-32, Magnetic Core Memory Systems (Figure 1-1). It is intended that this manual will contain all information required to properly operate and maintain the magnetic core memory system.

#### 1-2 SYSTEM DESIGNATION

The TCM-32 is a high-speed magnetic core memory system that stores data in binary form at specific locations or addresses within the system. The storage capacity and speed of any TCM-32 memory system is indicated in the designation. For example, a storage system designated TCM-32 512/30-3. 0/5. 0 is identifiable as a TCM-32 system having 512 words of storage, each word of which contains 30 bits. The "3. 0/5. 0" portion of the designation indicates that the system has a half-cycle (load or unload) operating time of 3  $\mu$ sec and a full-cycle (clear/write or read/regenerate) time of 5.0  $\mu$ sec.

#### 1-3 GENERAL DESCRIPTION

The basic storage elements of the TCM-32 system are toroidal ferrite cores. The cores are contained in a coincident-current core stack consisting of a number of mats or planes equal to the number of bits per word. A mat or plane contains a number of cores equal to the number of words of storage provided. Each core is capable of storing one bit of information; therefore, the total capacity of the memory equals the product of the number of cores per plane and the number of planes.

The TCM-32 magnetic core storage systems provide economical, efficient, fast-access storage. The memory is equipped to retain the magnetically stored information for an indefinite period even though primary power is removed.

The data signal interface between the TCM-32 and the external digital equipment with which it is used is achieved via flip-flop registers. This allows the address and the information signals from the external equipment to be specified as digital logic signals in the form of levels. Command signals are received by gates and are specified in the format of pulses.

Memory operation is controlled by internal timing circuits and occurs in response to one of several external command signals. Certain constraints exist between the timing of the command signals relative to the data signals; however, once the timing requirements are satisfied in the design of the system, memory operation is essentially independent of the associated equipment. Supervisory signals defining the status of the memory operation or signaling the completion of various phases of operation can be supplied to further augment the compatibility of the TCM-32 with the associated external equipment (Figure 1-1).

#### 1-4 BASIC ELEMENTS AND ORGANIZATION

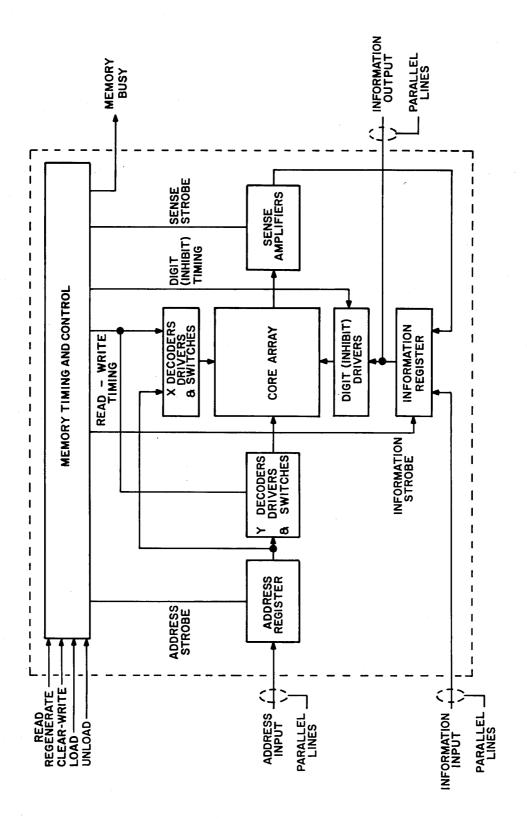

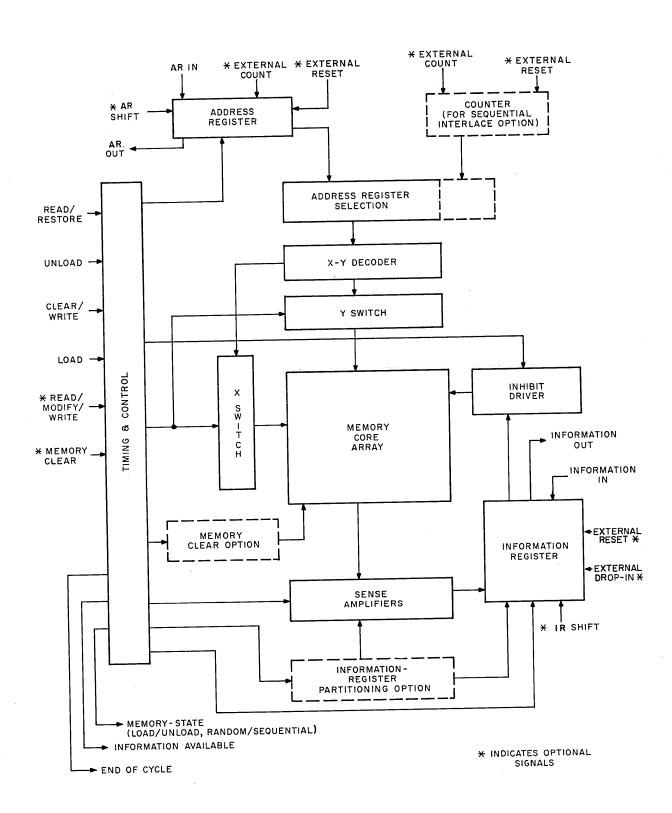

Figure 1-2 presents a simplified block diagram showing the basic elements and organization of a typical core memory system. In brief, the functions of these elements are as follows.

- a. Memory Timing and Control provides the sequence of pulses necessary to perform a specified operation in response to a given command (clear/write, read/regenerate, load, unload or read/modify/write). (This unit generates the necessary timing signals for both the internal and external requirements.)

- b. Address Register stores the specified address in binary form (static flip-flops) for a specified cycle. The outputs of the address register are used to drive the X and Y decoders.

- c. X and Y Decoders and Switches decode the contents of the address register to select only the one proper address. The selected switches

are set up to allow the drive current to read from or write into the ferrite cores. The current pulses are directed by the switches through the proper X and Y drive lines.

- d. <u>Core Stack</u> utilizes a conventional four-wire coincident-current wiring scheme. The construction and operation of the core stack is described in detail in Section III of this manual.

- e. <u>Information Register</u> stores the information, one word at a time, to be inserted into the memory during a clear/write or load cycle. The information register receives the output information of a selected address during read/regenerate or unload cycles. This register also provides double-rail outputs to the external equipment.

- f. <u>Sense Amplifiers</u> receive the output of selected cores, reject noise, and amplify the outputs to set the information register. One sense amplifier is required for each bit of the information word. The amplifiers employ time and amplitude discrimination to determine a ONE or a ZERO core output.

- g. <u>Inhibit Drivers</u> are controlled by the information register and timed by the inhibit timing pulse. Each plane or bit is selectively driven in the memory by its inhibit driver circuit during a write period. When a ZERO is to be written in the selected core, the inhibit driver produces a current pulse which acts in opposition to the selected drive current. If a ONE is to be written, the inhibit driver is gated off by the appropriate flip-flop in the information register.

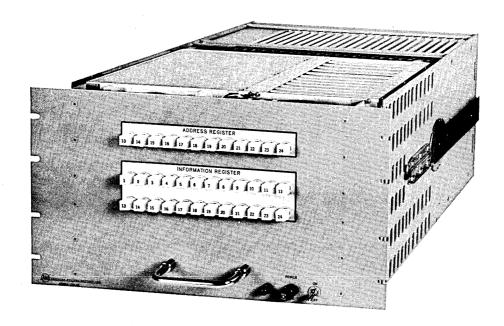

#### 1-4.1 Memory System Layout

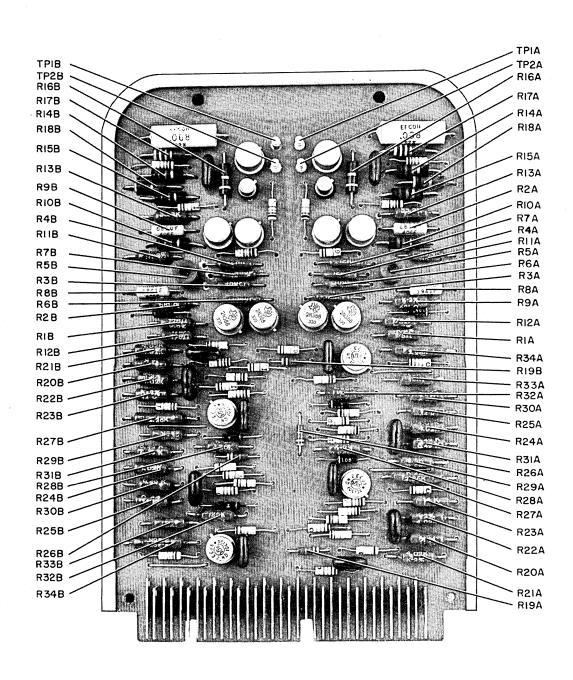

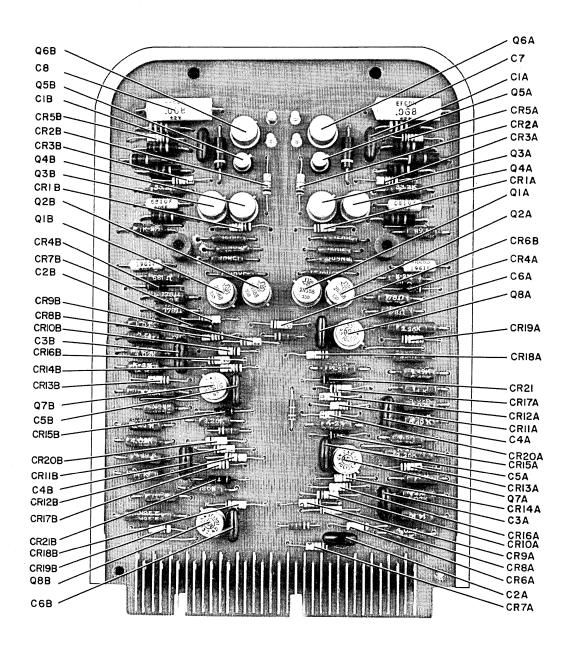

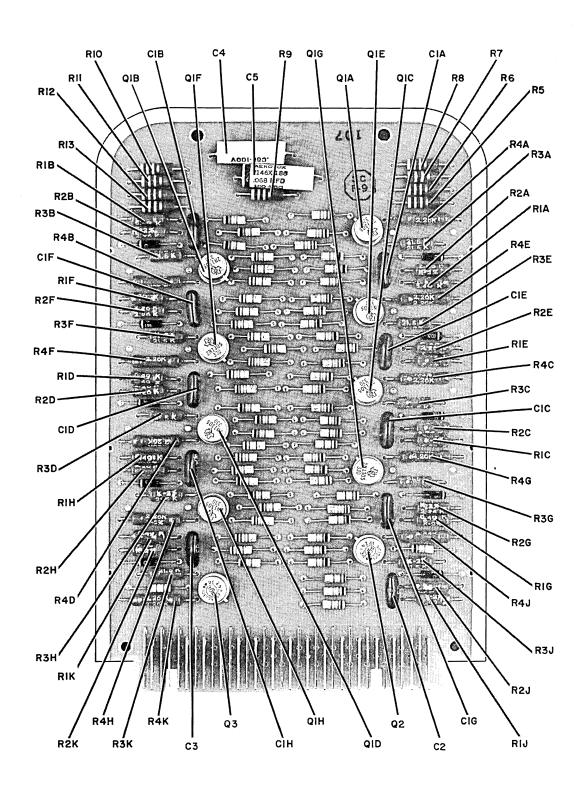

Figure 1-3 identifies the unit layout of the memory system. The memory system is mechanically designed for standard 19-inch relay rack mounting. Brief descriptions of each unit are listed below.

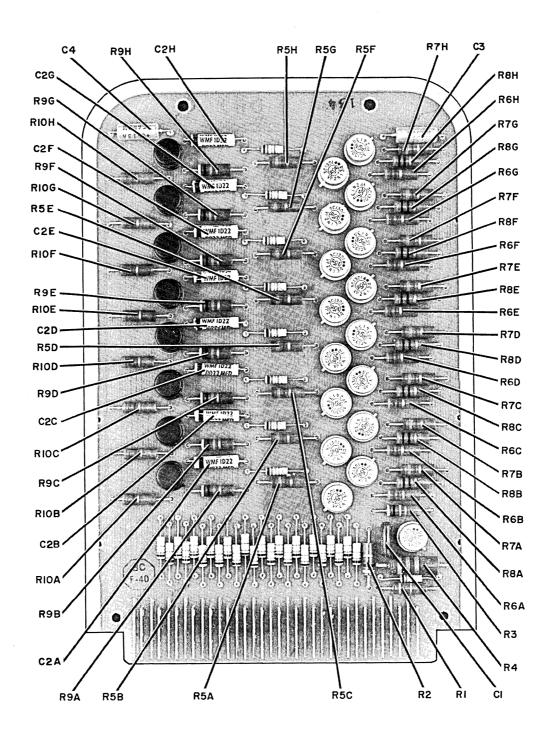

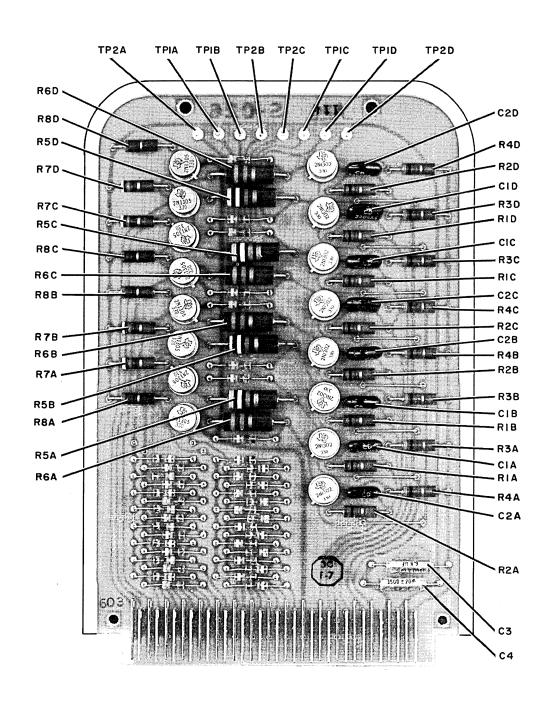

Unit 1 contains part of the information register, timing and control circuits, and partitioning option.

Unit 2 contains selection switches, current drivers, read-write gate driver, and inhibit drivers.

Unit 3 contains part of the information, and address registers. Unit 4 contains inhibit drivers, and address decoders.

Figure 1-2. Memory System, Block Diagram

Figure 1-3. Memory System Layout

#### 1-5 INPUT SIGNALS

The address register varies from 7 to 12 bits, depending on memory capacity (size). The minimum period of time and the time at which inputs must be present for a random-address operation are shown in the timing diagrams of Section III.

Clear/write command initiates a cycle which clears the cores at the address specified by the address register, and writes the information provided in the information register.

Read/regenerate initiates a cycle which reads the cores at the address specified by the address register and rewrites this information in the cores previously read. The information is held in the information register until another cycle is started. The size of the information register corresponds to the number of bits per word. Information is provided in parallel to this register and must be timed as indicated in the timing diagrams of Section III.

#### SECTION II SYSTEM INSTALLATION

#### 2-1 GENERAL

After unpacking the equipment, conduct a visual mechanical inspection to determine whether the equipment was damaged during shipment, and immediately report any damage to the carrier or shipping agency.

During positioning and installation of the equipment, do not disturb any factory adjustments. Check that the AC power switch, located on the front panel of the memory unit (Figure 1-1), is in the OFF position before making any electrical connections.

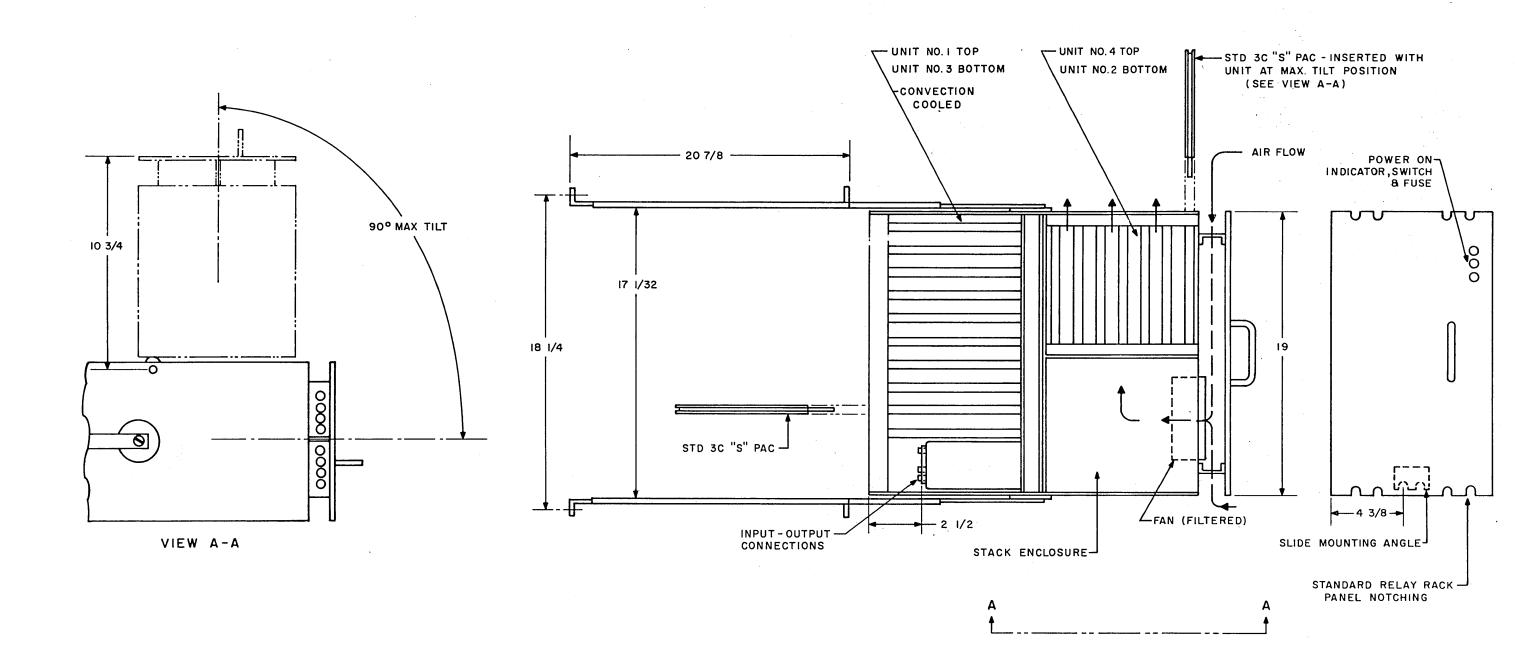

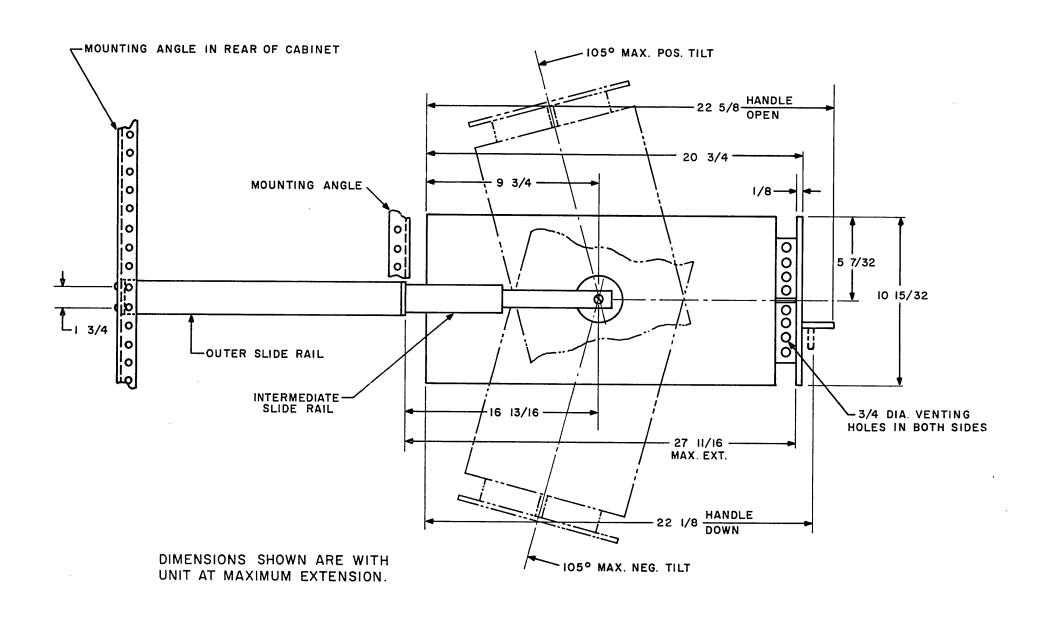

The system is shipped with the core matrix, all S-BLOC chassis, and 3C S-PACs prewired and properly secured in place. After completing the mechanical installation of the equipment in the rack, conduct a second inspection to ensure that all wiring and PACs are secured. Mechanical installation is illustrated in Figure 2-1.

#### 2-2 ELECTRICAL INTERCONNECTIONS

The wiring of connectors J-102 through J-107 are defined in Tables 2-1 through 2-6. The physical location of these connectors is shown in Figure 2-2; the pin numbering scheme is illustrated in Figure 2-3. A diagram showing the power wiring of the TCM-32 is presented in Figure 2-4. The AC and DC power connections should be provided via the mating connectors furnished by Computer Control Company. Refer to the pin connections in Figure 2-4 and note that two -18 volt connections are shown. These connections should not be connected in P101 but wired as separate leads back to the power supply. This will utilize the filtering capacitors in the power supply and reduce noise on the -18 volt logic buses due to inhibit pulse current.

Figure 2-1. Installation Drawing (Sheet 1 of 2)

Figure 2-1. Installation Drawing (Sheet 2 of 2)

MATING CONNECTORS (SHIPPED WITH TCM-32)

- 1. CONNECTOR, DD-50P 3C PART NO. 941 105 001

- 2. PLUG, MRA-14S-JTC-H 3C PART NO. 941 114 001

- 3. PLUG, M4S-LS 3C PART NO. 941 115 001

#### NOTES:

- 1. UNIT WEIGHT (EMPTY) APPROX. 40 LB

- 2. MAX. PAC EXTRACTION FORCE REQD 20 LB

- 3. POWER INPUT -115 V AC FUSED ON FRONT PANEL. DC INPUT INTERLOCKED THRU AC ACTUATED RELAY.

- 4. MEMORY NORMALIZER BOARD (MN) IS LOCATED BEHIND CONNECTORS J102, J103, J104, IN UNIT 1.

- INDICATOR POWER SUPPLY (WHEN INCLUDED AS AN OPTION) IS LOCATED BEHIND CONNECTORS J105, J106, J107, IN UNIT 3.

Figure 2-2. Connector Detail

CONNECTOR TYPE: CANNON DD-50 (NOT TO SCALE)

Figure 2-3. Pin Numbering, Connectors J-102 through J-107

Figure 2-4. TCM-32 Power Wiring Diagram

TABLE 2-1. WIRING CONNECTOR J-102

(Connector location is found in Figure 2-2 Figure 2-3 shows pin numbering)

| Pin<br>Number | Signal              | Function       | Pin<br>Number | Signal      | Function       |

|---------------|---------------------|----------------|---------------|-------------|----------------|

|               | I-1                 | Information In | 26            | <u>I-13</u> | Information In |

| 1             | $\frac{1-1}{I-1}$   | Information In | 27            | I-14        | Information In |

| 2             | I-1                 | Information In | 28            | <u>I-14</u> | Information In |

| 3             | $\frac{1-2}{1-2}$   | Information In | 29            | I-15        | Information In |

| 4             | I-3                 | Information In | 30            | I-15        | Information In |

| 5             | $\frac{1-3}{1-3}$   | Information In | 31            | I-16        | Information In |

| 6             | I-4                 | Information In | 32            | <u>I-16</u> | Information In |

| 7             | $\frac{1-4}{1-4}$   | Information In | 33            | I-17        | Information In |

| 8             | I-5                 | Information In | 34            | <u>I-17</u> | Information In |

| 9             | 1-5<br>1-5          | Information In | 35            | I-18        | Information In |

| 10            | I-6                 | Information In | 36            | <u>I-18</u> | Information In |

| 11            | $\frac{1-6}{1-6}$   | Information In | 37            | I-19        | Information In |

| 12            | I-7                 | Information In | 38            | I-19        | Information In |

| 13            | $\frac{1-7}{1-7}$   | Information In | 39            | I-20        | Information In |

| 14            | I-8                 | Information In | 40            | <u>I-20</u> | Information In |

| 15            | $\frac{1-8}{1-8}$   | Information In | 41            | I-21        | Information In |

| 16            | I-9                 | Information In | 42            | <u>I-21</u> | Information In |

| 17            | $\frac{1-9}{1-9}$   | Information In | 43            | I-22        | Information In |

| 18            | I-10                | Information In | 44            | <u>1-22</u> | Information In |

| 19            | $\frac{1-10}{1-10}$ | Information In | 45            | I-23        | Information In |

| 20            | I-11                | Information In | 46            | <u>1-23</u> | Information In |

| 21            | $\frac{1-11}{I-11}$ | Information In | 47            | I-24        | Information In |

| 22            | I-12                | Information In | 11            | <u>I-24</u> | Information In |

| 23            | I-12                | _              | 11            |             | Signal Ground  |

| 24            | I-12                | Information In | 11            |             | Chassis Ground |

| 25            | 1-13                | 111101111101   |               |             |                |

|               |                     |                |               |             |                |

|               |                     |                |               |             |                |

|               |                     |                |               |             |                |

|               |                     |                |               |             |                |

|               |                     |                |               |             |                |

TABLE 2-2.

WIRING CONNECTOR J-103

| WIRING CONNECTOR J-103 |        |                 |               |                |                 |

|------------------------|--------|-----------------|---------------|----------------|-----------------|

| Pin<br>Number          | Signal | Function        | Pin<br>Number | Signal         | Function        |

| 1                      | IR-Ì   | Information Out | 26            | ĪR-13          |                 |

| 2                      | IR-I   | Information Out | 27            | IR-14          | Jacob Out       |

| 3                      | IR-2   | Information Out | 28            | IR-14          | Mation Out      |

| 4                      | IR-2   | Information Out | 29            | IR-15          | Information Out |

| 5                      | IR-3   | Information Out | 30            | IR-15          | Information Out |

| 6                      | IR-3   | Information Out | 31            | IR-16          | Information Out |

| 7                      | IR-4   | Information Out | 32            | IR-16          | Information Out |

| 8                      | IR-4   | Information Out | 33            | IR-17          | Information Out |

| 9                      | IR-5   | Information Out | 34            | IR-17          | Information Out |

| 10                     | IR-5   | Information Out | 35            | IR-17          | Information Out |

| 11                     | IR-6   | Information Out | 36            | IR-18          | Information Out |

| 12                     | IR-6   | Information Out | 37            | IR-19          | Information Out |

| 13                     | IR-7   | Information Out | 38            | IR-19<br>IR-19 | Information Out |

| 14                     | IR-7   | Information Out | 39            | IR-19<br>IR-20 | Information Out |

| 15                     | · IR-8 | Information Out | 40            | IR-20<br>IR-20 | Information Out |

| 16                     | IR-8   | Information Out | 41            | IR-20          | Information Out |

| 17                     | IR-9   | Information Out | 42            | IR-21<br>IR-21 | Information Out |

| 18                     | IR-9   | Information Out | 43            | IR-21<br>IR-22 | Information Out |

| 19                     | IR-10  | Information Out | 44            | IR-22<br>IR-22 | Information Out |

| 20                     | IR-10  | Information Out | 45            | IR-22          | Information Out |

| 21                     | IR-11  | Information Out | 46            | IR-23          | Information Out |

| 22                     | IR-11  | Information Out | 47            | IR-24          | Information Out |

| 23                     | IR-12  | Information Out | 48            | IR-24<br>IR-24 | Information Out |

| 24                     | IR-12  | Information Out | 49            | IK-24          | Information Out |

| 25                     | IR-13  | Information Out | 50            |                | Signal Ground   |

|                        |        |                 | 30            |                | Chassis Ground  |

|                        |        |                 |               |                |                 |

|                        |        |                 |               |                |                 |

|                        |        |                 |               | 1.             |                 |

|                        |        |                 |               | }              |                 |

|                        |        |                 |               |                |                 |

|                        |        |                 |               |                |                 |

|                        |        | U_              |               |                | 1               |

## TABLE 2-3. WIRING CONNECTOR J-104

| Pin<br>Number | Function                                   | Remarks                                       |

|---------------|--------------------------------------------|-----------------------------------------------|

| 1             | Input: Read/Regenerate (SIG)               | l and 2: Twisted Pair                         |

| 2             | Input: Read/Regenerate (GND)               |                                               |

| 3             | Input: Clear/Write (SIG)                   | 3 and 4: Twisted Pair                         |

| 4             | Input: Clear/Write (GND)                   |                                               |

| 5             | Input: Unload Buffer (SIG)                 | 5 and 6: Twisted Pair                         |

| 6             | Input: Unload Buffer (GND)                 |                                               |

| 7             | Input: Load Buffer (SIG)                   | 7 and 8: Twisted Pair                         |

| 8             | Input: Load Buffer (GND)                   |                                               |

| 9             | Input: Random/Sequential<br>Operation      | -6 V: Random<br>0 V: Sequential               |

| 10            | Input: Memory Clear (SIG)                  | 10 and 11: Twisted Pair                       |

| 11            | Input: Memory Clear (GND)                  |                                               |

| 12            | Input: Reset Unload Counter                |                                               |

| 13            | Input: Reset Load Counter                  | (Address register)                            |

| 14            | Input: Reset Information<br>Register (SIG) | Pulse: -6 V to 0 V 14 and 15:<br>Twisted Pair |

| 15            | Input: Reset Information<br>Register (GND) |                                               |

| 16            | Input: Drop-in (SIG)                       | Pulse: -6 V to 0 V 16 and 17:<br>Twisted Pair |

| 17            | Input: Drop-in (GND)                       |                                               |

| 18            | Input: Read/Modify/Write                   | RMW                                           |

| 19            | Input: Load Counter<br>(Advance SIG)       | Pulse: -6 V to 0 V 19 and 20:<br>Twisted Pair |

| 20            | Input: Load Counter<br>(Advance GND)       |                                               |

| 21            | Input: Unload Counter<br>(Advance SIG)     | Pulse: -6 V to 0 V 21 and 22:<br>Twisted Pair |

| 22            | Input: Unload Counter<br>(GND)             |                                               |

| 23            | Input: Address Register<br>Strobe (SIG)    | Pulse: -6 V to 0 V Twisted Pair               |

|               |                                            |                                               |

TABLE 2-3. (Cont) WIRING CONNECTOR J-104

| WIRING CONNECTOR J-104 |                                         |                               |  |  |  |

|------------------------|-----------------------------------------|-------------------------------|--|--|--|

| Pin<br>Numbe           | r Function                              | Remarks                       |  |  |  |

| 24                     | Input: Address Register<br>Strobe (GND) |                               |  |  |  |

| 25                     | Input: Address Register<br>Shift (SIG)  | 25 and 26: Twisted Pair       |  |  |  |

| 26                     | Input: Address Register<br>Shift (GND)  |                               |  |  |  |

| 27                     | Input: Information Shift (SIG)          | 27 and 28: Twisted Pair       |  |  |  |

| 28                     | Input: Information Shift (GND)          |                               |  |  |  |

| 29                     | Input: Information Register             | Zone A                        |  |  |  |

| 30                     | Input: Information Register             | Zone B                        |  |  |  |

| 31                     | Input: Information Register             | Zone C partitioning option    |  |  |  |

| 32                     | Input: Information Register             | Zone D                        |  |  |  |

| 33                     |                                         | Wired Spare                   |  |  |  |

| 34                     |                                         | Wired Spare Wired Spare       |  |  |  |

| 35                     |                                         | Wired Spare Wired Spare       |  |  |  |

| 36                     |                                         | 1                             |  |  |  |

| 37                     |                                         | Wired Spare                   |  |  |  |

| 38                     | Output: End of Cycle                    | Pulse: -6 V to 0 V 38 and 39: |  |  |  |

| 39                     | Output: End of Cycle                    | Twisted Pair                  |  |  |  |

| 40                     | Output: Information Ready (SIG)         | Pulse: -6 V to 0 V 40 and 41: |  |  |  |

| 41                     | Output: Information Ready (GND)         | Twisted Pair                  |  |  |  |

| 42                     | Random Access                           | -6 V                          |  |  |  |

| 43                     | Sequential Access                       | -6 V                          |  |  |  |

| 44                     | Load Mode                               | -6 V                          |  |  |  |

| 45                     | Unload Mode                             | -6 V                          |  |  |  |

| 46                     | Power                                   | +12 V                         |  |  |  |

| 47                     | Power                                   | -6 V                          |  |  |  |

| 48                     | Power                                   | -18 V                         |  |  |  |

| 49                     |                                         | Signal Ground                 |  |  |  |

| 50                     |                                         | Chassis Ground                |  |  |  |

TABLE 2-4. WIRING CONNECTOR J-105

|   | WIRING CONNECTOR J-103 |        |                  |               |        |                  |  |

|---|------------------------|--------|------------------|---------------|--------|------------------|--|

|   | Pin<br>Number          | Signal | Function         | Pin<br>Number | Signal | Function         |  |

| = |                        | A-1    | Address Reg. In  | 26            | AR-7*  | Address Reg. Out |  |

|   | 1 2                    | A-2    | Address Reg. In  | 27            | AR-8   | Address Reg. Out |  |

|   | 3                      | A-3    | Address Reg. In  | 28            | AR-8*  | Address Reg. Out |  |

|   | 4                      | A-4    | Address Reg. In  | 29            | AR-9   | Address Reg. Out |  |

|   | 5                      | A-5    | Address Reg. In  | 30            | AR-9*  | Address Reg. Out |  |

|   | 6                      | A-6    | Address Reg. In  | 31            | AR-10  | Address Reg. Out |  |

|   | 7                      | A-7    | Address Reg. In  | 32            | AR-10* | Address Reg. Out |  |

|   | 8                      | A-8    | Address Reg. In  | 33            | AR-11  | Address Reg. Out |  |

|   | 9                      | A-9    | Address Reg. In  | 34            | AR-11* | Address Reg. Out |  |

|   | 10                     | A-10   | Address Reg. In  | 35            | AR-12  | Address Reg. Out |  |

|   | 11                     | A-11   | Address Reg. In  | 36            | AR-12* | Address Reg. Out |  |

|   | 12                     | A-12   | Address Reg. In  | 37            | ARU-l* | Unload AR Out    |  |

|   | 13                     | AR-l   | Address Reg. Out | 38            | ARU-2* | Unload AR Out    |  |

|   | 14                     | AR-1*  | _                | 11            | ARU-3* | Unload AR Out    |  |

|   | 15                     | AR-2   | Address Reg. Out | 11            | ARU-4* | Unload AR Out    |  |

|   | 16                     | ĀR-2*  | _                | 11            | ARU-5* | Unload AR Out    |  |

|   | 17                     | AR-3   | Address Reg. Out | 42            | ARU-6* | Unload AR Out    |  |

|   | 18                     | AR-3*  | Address Reg. Out | 43            | ARU-7* | Unload AR Out    |  |

|   | 19                     | AR-4   | Address Reg. Out | 44            | ARU-8* | Unload AR Out    |  |

|   | 20                     | AR-4*  | Address Reg. Out | 45            | ARU-9* | Unload AR Out    |  |

|   | 21                     | AR-5   | Address Reg. Out | t 46          | ARU-10 |                  |  |

|   | 22                     | AR-5   | Address Reg. Ou  | t   47        | ARU-11 | <b>!</b>         |  |

|   | 23                     | AR-6   | Address Reg. Ou  | t   48        | ARU-12 | * Unload AR Out  |  |

|   | 24                     | AR-6   | Address Reg. Ou  | t   49        |        |                  |  |

|   | 25                     | AR-7   | Address Reg. Ou  | t   50        |        |                  |  |

|   |                        |        |                  |               |        |                  |  |

|   |                        |        |                  |               |        |                  |  |

|   |                        |        |                  |               |        |                  |  |

|   |                        |        |                  |               |        |                  |  |

|   |                        |        |                  |               |        |                  |  |

\*ARU and  $\overline{AR}$  signals on request only

TABLE 2-5.

WIRING CONNECTOR J-106

| WIRING CONNECTOR J-106 |             |                |               |                                |                |

|------------------------|-------------|----------------|---------------|--------------------------------|----------------|

| Pin<br>Number          | Signal      | Function       | Pin<br>Number | Signal                         | Function       |

| 1                      | I-25        | Information In | 26            | Ī-37                           | Information In |

| 2                      | I-25        | Information In | 27            | I-38                           | Information In |

| 3                      | I-26        | Information In | 28            | I-38                           | Information In |

| 4                      | <u>I-26</u> | Information In | 29            | I-39                           | Information In |

| 5                      | I-27        | Information In | 30            | I-39                           | Information In |

| 6                      | I-27        | Information In | 31            | I-40                           | Information In |

| 7                      | I-28        | Information In | 32            | $\frac{1-10}{I-40}$            | Information In |

| 8                      | I-28        | Information In | 33            | I-41                           | Information In |

| 9                      | I-29        | Information In | 34            | $\frac{\overline{I-41}}{I-41}$ | Information In |

| 10                     | I-29        | Information In | 35            | I-42                           | Information In |

| 11                     | I-30        | Information In | 36            | I-42                           | Information In |

| 12                     | I-30        | Information In | 37            | I-43                           | Information In |

| 13                     | I-31        | Information In | 38            | I-43                           | Information In |

| 14                     | I-31        | Information In | 39            | I-44                           | Information In |

| 15                     | I-32        | Information In | 40            | <u>I-44</u>                    | Information In |

| 16                     | I-32        | Information In | 41            | I-45                           | Information In |

| 17                     | I-33        | Information In | 42            | I-45                           | Information In |

| 18                     | I-33        | Information In | 43            | I-46                           | Information In |

| 19                     | I-34        | Information In | 44            | <u>1-46</u>                    | Information In |

| 20                     | I-34        | Information In | 45            | I-47                           | Information In |

| 21                     | I-35        | Information In | 46            | I-47                           | Information In |

| 22                     | I-35        | Information In | 47            | I-48                           | Information In |

| 23                     | I-36        | Information In | 48            | <u>I-48</u>                    | Information In |

| 24                     | I-36        | Information In | 49            |                                | Signal Ground  |

| 25                     | I-37        | Information In | 50            |                                | Chassis Ground |

|                        |             |                |               |                                | onabels Ground |

|                        |             |                |               |                                |                |

|                        |             |                |               |                                |                |

|                        |             |                |               |                                |                |

| _                      |             |                |               |                                |                |

|                        |             |                |               |                                |                |

|                        | <u> </u>    |                |               |                                |                |

TABLE 2-5. (Cont)

WIRING CONNECTOR J-107

|               |                       | W 11(11 )       |               |        |                 |

|---------------|-----------------------|-----------------|---------------|--------|-----------------|

| Pin<br>Number | Signal                | Function        | Pin<br>Number | Signal | Function        |

|               | IR-25                 | Information Out | 26            | IR-37  | Information Out |

| 1             | IR-25<br>IR-25        | Information Out | 27            | IR-38  | Information Out |

| 2             | IR-25<br>IR-26        | Information Out | 28            | ĪR-38  | Information Out |

| 3             | IR-26                 | Information Out | 29            | IR-39  | Information Out |

| 4             | IR-20<br>IR-27        | Information Out | 30            | IR-39  | Information Out |

| 5             | IR-27<br>IR-27        | Information Out | 31            | IR-40  | Information Out |

| 6             | IR-27                 | Information Out | 32            | IR-40  | Information Out |

| 7             | IR-28<br>IR-28        | Information Out | 33            | IR-41  | Information Out |

| 8             | IR-28                 | Information Out | 34            | IR-41  | Information Out |

| 9             | IR-29<br>IR-29        | Information Out | 35            | IR-42  | Information Out |

| 10            | IR-29<br>IR-30        | Information Out | 36            | IR-42  | Information Out |

| 11            | IR-30<br>IR-30        | Information Out | 37            | IR-43  | Information Out |

| 12            | IR-30                 | Information Out | 38            | IR-43  | Information Out |

| 13            | $\frac{1R-31}{IR-31}$ | Information Out | 39            | IR-44  | Information Out |

| 14            | IR-31                 | Information Out | 40            | IR-44  | Information Out |

| 15            | $\frac{1R-32}{IR-32}$ | Information Out | 41            | IR-45  | Information Out |

| 16            | IR-32                 | Information Out | 42            | IR-45  | Information Out |

| 17            | $\frac{IR-33}{IR-33}$ | Information Out | 43            | IR-46  | Information Out |

|               | IR-34                 | Information Out | 44            | IR-46  | Information Out |

| 19            | IR-34<br>IR-34        | Information Out | 45            | IR-47  | Information Out |

|               | IR-35                 | Information Out | 46            | IR-47  | Information Out |

| 21            | IR-35                 | Information Out | 47            | IR-48  | Information Out |

| 22            | IR-36                 | Information Out | 48            | IR-48  | Information Out |

| 23            | IR-36                 | Information Out | 49            |        | Signal Ground   |

| 24            | IR-37                 | Information Out | 50            |        | Chassis Ground  |

| 25            | 1K-31                 | 11110111101111  |               |        |                 |

|               |                       | **              |               |        |                 |

|               |                       |                 |               |        |                 |

|               |                       |                 |               |        |                 |

|               |                       |                 |               |        |                 |

|               |                       |                 |               |        |                 |

|               |                       |                 |               |        |                 |

|               |                       |                 |               |        |                 |

#### SECTION III PRINCIPLES OF OPERATION

#### 3-1 PRINCIPLES OF MAGNETIC CORE MEMORIES

#### 3-1.1 Magnetic Core Storage

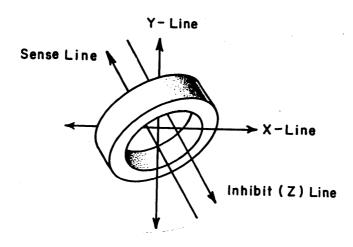

The memory core stack, housed in the magnetic core unit, is a matrix configuration of individual small (50 mils O.D., 30 mils I.D.) ferrite cores. The cores are arranged in identical planes, each plane having X-rows and Y-columns. Basically, the ferrite core is a 1-bit storage element in the form of a ferrite ceramic ring that can be magnetically saturated to either positive or negative flux density. The ferrite material retains a large part of the magnetic flux developed at the time the core is saturated which is an important characteristic of the core. The time required to switch a core from one polarity or state to another is primarily dependent on the core material and size. Consequently, cores measuring only millimeters in diameter are used in the memory core array to permit fast switching speeds.

A similarity exists between the magnetic core and the flip-flop in that both provide storage for one bit of data. The two extremes of saturation in a magnetic core represent ZERO and ONE, as do the two stable states of a flip-flop. A core can be set to a ONE state by the application of a current pulse of similar magnitude applied in the opposite direction. Similarly, a flip-flop is set or reset by applying pulses to the appropriate inputs. Both the magnetic core and the flip-flop provide memory of the last pulse applied, but the core does so without requiring power to hold its state.

The ferrite core has a nearly rectangular hysteresis loop. The hysteresis loop is a graphical representation of the flux density produced in a magnetic material, plotted against the magnetizing force that produces it. Figure 3-1 is a simplified drawing showing the generation of a typical ferrite

Figure 3-1. Ferrite Core Hysteresis Loop

core hysteresis loop. Starting with an unmagnetized core, an increase in magnetizing current (H) increases the flux density (B) along the S-shaped curve (3-1A). The flux density levels off when the core is saturated, and any additional current applied does not appreciably increase the flux density because the core material is supporting as much flux as it can. As the current is decreased, then made to flow in the opposite direction, the flux does not collapse along the same line (3-1B); and most of the flux remains even after the current has fallen to zero. The amount of flux actually remaining is a function of the retentivity of the magnetic material. As a magnetizing current is applied in the opposite direction, it has little effect on the flux level until the current reaches the knee of the hysteresis loop. (Note that a certain amount of current is required to overcome the residual magnetism to return the core to a neutral condition.)

A slight increase in current beyond the knee of the curve switches the core rapidly to negative saturation (3-1C). The point on the curve representing the amount of current required to change the state of the core is termed the coercive current. When the negative magnetizing current is removed, most of the flux is retained as before (3-1D). Note that the original sweep from a magnetically neutral condition is never repeated (3-1E). A memory core in coincident-current use is never in a neutral condition, but is switched from one saturated state to the other. The core is thus an extremely useful binary component because it can exist in either of two stable states and can switch rapidly from one to the other.

For any given toroidal magnetic core, the necessary magnetomotive force required to effect switching is a function of the product of the number of turns of wire and the current driven through those turns. It is not economically feasible to wind multiple turns of wire around the small toroidal cores used in core memories; rather the number of turns is reduced to two, one in each of the perpendicular driving coordinates, and the current in these coordinate wires is of such a magnitude as to cause switching (rapid flux change) to occur.

In addition to the perpendicular (X and Y) coordinate selection lines, each core is also threaded by two other wires, each of which passes through every core in a plane. One is the sense winding, which detects flux-change

due to switching of a core and thus provides a readout signal from the plane. The other winding is the inhibit winding which is used, as its name suggests, to inhibit or prevent the writing of a ONE into the core, thereby causing ZERO to be stored. A single memory core, with its associated control windings is illustrated in Figure 3-2.

A disadvantage of the memory core is that it does not provide a static indication of its state, as does a flip-flop. To obtain an indication of the condition of the flux in a memory core, the state of the core must be switched.

Figure 3-2. Core Control Windings

### 3-1.2 Addressing

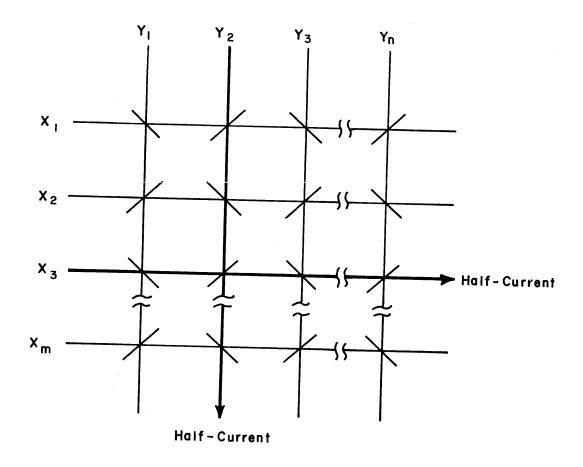

The complete core stack for a magnetic core unit consists of a number of individual matrices or planes. Each plane contains memory cores assembled in a rectangular configuration. The memory cores are threaded by X- and Y-lines in each plane so that one memory core is physically located at each junction of an X-line and Y-line.

As previously stated, pulses of current applied along the X- and Y-lines switch a memory core from one state to another. If one-half of the current required to switch a core is applied along the X-line, and one-half of the necessary current is applied along the Y-line, the core situated at the

junction of the energized X- and Y-lines will receive the full switching current. This type of operation is termed coincident-current operation.

A coincident-current magnetic core memory depends upon the coincidence of two half-currents to read data from or to write data into the cores. Two additive half-current pulses will set the core to the ONE state, while two half-current pulses applied in the opposite direction will reset the core to the ZERO state. A core with two half-current inputs is essentially an AND circuit requiring that half-current be applied to both X- and Y-lines in the same direction to change the state of the flux at the core. A half-current applied to one line without a similar half-current applied to the other line has no effect on the core.

Only one X-line and one Y-line of a plane are energized during a single cycle, and only that core situated at the junction of the activated X-and Y-lines will respond to the coincident half-current pulses. Therefore, only one core in each plane will be affected during a single cycle. A simplified diagram of coincident-current selection of a memory core is illustrated in Figure 3-3. In effect, the X-line selects one row (X-row), and the Y-line selects one column (Y-column).

In coincident-current memories, the X- and Y-lines are wired in series through all planes of the memory core array. Thus each X-line and each Y-line threads corresponding rows or columns of cores in all memory planes. Energizing one of the X-lines (designated  $X_1$  through  $X_m$  in Figure 3-3) supplies a half-current pulse to the appropriate row of cores in every plane. Similarly, energizing one of the Y-lines (designated  $Y_1$  through  $Y_n$ ), supplies a half-current pulse to the appropriate column of cores in every plane. When pulses occur simultaneously on two lines (X and Y), they select the same core position in each of the planes. Therefore, the X- and Y-lines select a word in the memory core array and enable read or write operations.

Figure 3-3. Coincident-Current Selection

# 3-1.3 Information Sensing

Sense lines allow the reading of information stored in the cores. One sense line (Figure 3-2) is threaded through all memory cores of each plane.

To read any of the words stored in memory, half-currents in the proper direction are generated in the selected X- and Y-lines (Figure 3-3). The read half-currents combine at the coincident junction of the X- and Y-lines to change the state of the affected core in each memory plane. If the affected core is storing a ONE at that instant, the effect of the read half-currents will change the state of the core to ZERO. If the core was previously in the ZERO state, the read half-currents will have no effect on the core. When the core is switched from the ONE to the ZERO state, the rapid

change in flux from positive saturation to negative saturation induces a voltage pulse in the corresponding sense line. Therefore, the presence of a voltage pulse in the sense line during the read operation indicates that a ONE had been stored in the indicated core. If no voltage pulse occurs in a sense line during read operation, a ZERO is indicated. The sense lines designated  $S_{\rm O}$  through  $S_{\rm k}$  in the memory core stack are connected to sense amplifiers. A ONE input to any of the sense amplifiers is amplified and applied to the information register. Thus, output data is transferred from its storage location in the core stack to the information register.

#### 3-1.4 Writing

Inhibit lines are used to enable a computer word or instruction to be written into memory at a selected address location. A single inhibit line is threaded through each memory core in a plane (Figure 3-2), and each plane of the magnetic core unit requires an individual inhibit line.

To write information into memory, half-current pulses in the direction opposite to those generated for read operation are applied to the selected X- and Y-coincident junction to switch the affected core in each memory plane.

Since all the cores at the selected address have been cleared to the ZERO state prior to the application of the write half-currents, the write half-currents operate to switch all cores to the ONE state. If the incoming data dictates that a ZERO is to be written into a specific core, some means must be used to prevent the core from switching to the ONE state when the write half-currents are generated. This is accomplished by the inhibit (Z) lines designated  $Z_1$  through  $Z_k$ . An inhibit pulse, when transmitted through the inhibit line of the memory plane at the same time that the write half-currents are applied through the X- and Y-lines, prevents the writing of a ONE because the inhibit current subtracts from X- and Y-write current.

The inhibit pulse is of the same magnitude but of the opposite polarity to the write half-current pulses. Therefore, the inhibit pulse directly cancels the effect of one write half-current pulse. The net effect of the two write half-current pulses and an inhibit pulse, is equivalent to a single write

half-current pulse on the addressed core. This prevents the core from switching from the ZERO to the ONE state.

Information to be written into memory is stored in the information register prior to being transferred to the memory core stack. During the transfer operation, a binary ONE from the register flip-flop will prevent the generation of an inhibit pulse whereas a binary level ZERO from the register flip-flop allows an inhibit pulse to be generated. In this way information is rewritten (or new information is written) into the selected memory location exactly as it appears in the information register.

## 3-1.5 Information Retention

The magnetic core unit does not require power to provide static memory capability. A pulse of power is required to switch the cores from one state to another, but not to hold cores in their respective states. All cores remain in the state to which they have been switched, because of the retentivity of the core magnetic material. If power is removed or lost without a severe transient pulse being generated, the core stack retains the stored information indefinitely.

# 3-2 GENERAL SPECIFICATIONS, TCM-32 MEMORY SYSTEM

## Capacity:

Words: 128, 256, 512, 1024, 2048, and 4096

Word Length: 8 to 48 bits (in 2-bit increments)

### Cycle Time:

Full Cycle: 5 μsec Half Cycle: 3 μsec Access: 2.3 μsec

## Modes of Operation:

Clear/Write

Read/Regenerate

Load

Unload

Read/Modify/Write

### Operating Temperature:

0°C to 50°C

### Humidity:

95% without condensation

### Power:

+12 VDC

-6 VDC

As supplied by S-PAC

Series RP-31 or equivalent

-18 VDC

### Options:

Read/Modify/Write

Sequential Addressing

Random-Sequential Addressing

Sequential-Interlace Addressing

Serial Address-Register Operation

Memory Clear

Information-Register Partitioning

Serial Information-Register Operation

### Physical Description:

Standard 19-in. drawer mount

10-1/2 in. high

20-3/4 in. deep

135 lb maximum

## Input Signal Specifications:

- a. All input circuits are designed to operate between 0 V and -6 V.

- b. All inputs are diode coupled/isolated and provide noise rejection margins of 1.5 V minimum.

- c. Each input requires a flow of approximately 2.5 ma, when the driving source is at ground and approximately 0 ma when the driving source is at -6 V.

- d. Each input that is not strobed or clocked must have a maximum rise time of 0.2  $\mu$ sec (10% amplitude point to 90% amplitude point). Minimum pulse width is 0.3  $\mu$ sec.

e. Those inputs which are clocked or strobed may rise at any desired rate as long as they fulfill specified timing requirements.

## Output Signal Specifications:

- a. Outputs will swing between 0 V and -6 V. All outputs clamped.

- b. All outputs are capable of driving 400  $\mu\mu$ f of stray capacitance in addition to 20 ma from ground.

- c. Typical rise times are 0.1  $\mu$ sec. Typical fall times are 0.15  $\mu$ sec.

# 3-3 TCM-32 FUNCTIONAL DESCRIPTION

The basic function of the TCM-32 memory system is the magnetic core storage of information which is fed to the memory by an external system (typically, a computer) and the restoration of the information to the external system upon command. A block diagram of the TCM-32 memory is presented in Figure 3-4, to which this functional description is referenced.

## 3-3.1 Address Register

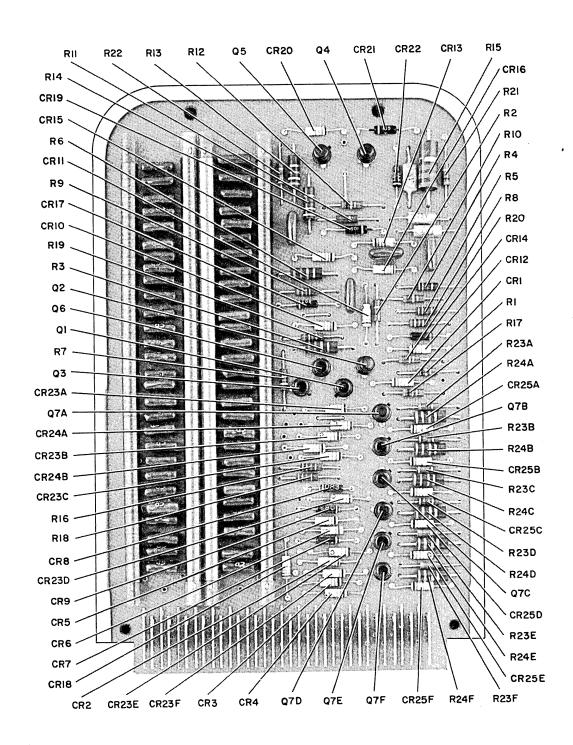

The address register (AR) of the memory system is composed of MF-30 flip-flops. The AR stores the selected address in static flip-flops for a specified cycle, and the AR outputs drive the X- and Y-decoders. In any of the optional sequential-addressing arrangements, the AR is wired and operated as a counter.

# 3-3.2 X- and Y-Decoders, Switches, and Drivers

The X- and Y-decoders and switches decode the contents of the AR so that only one memory location is selected. A specific address input activates one X-row of memory cores and one Y-column of memory cores, as shown in Figure 3-3. The selected switches allow the drive currents to read from and write into the corresponding cores of the memory array. (The current pulses are generated from temperature-compensated, dynamically regulated drivers, the outputs of which are essentially independent of supply voltages.)

Figure 3-4. TCM-32 Memory System, Block Diagram

## 3-3.3 Memory Timing and Control

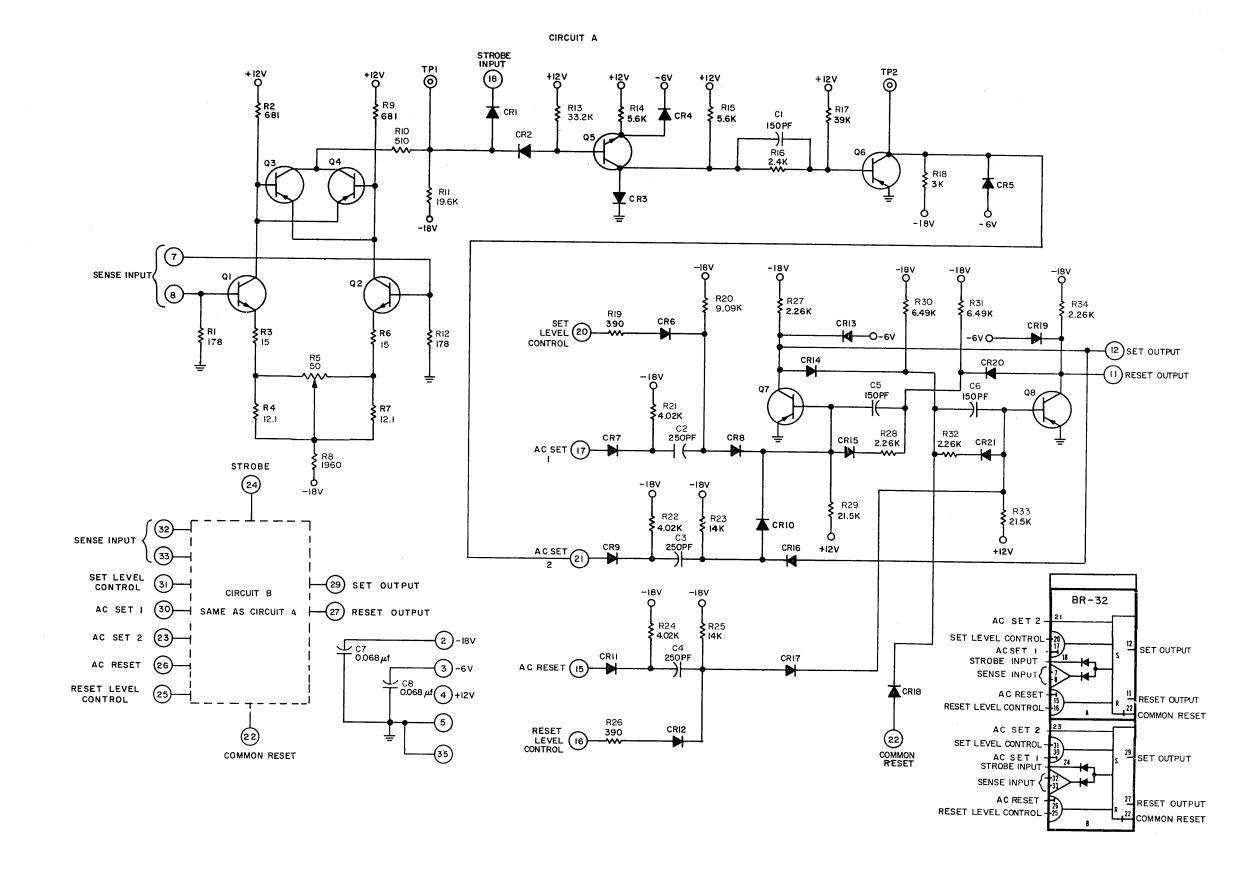

The memory timing and control circuits provide the sequence of pulses necessary to carry out the specific operation (read/regenerate, clear/write, load, unload, and optionally, read/modify/write). Timing and control also generates the memory-busy signal, memory-state indicator signal, an information-available marker, and an end-of-cycle marker pulse.

### 3-3.4 Memory Core Stack

The principles of the memory core stack are described in detail in Section 3-1. The core stack utilizes a four-wire coincident-current wiring scheme and consists of a number of individual planes, each of which contains magnetic cores assembled in an X- and Y-configuration.

## 3-3.5 <u>Information Register</u>

The information register (IR) stores one information word which is to be inserted into the memory during a load or clear/write cycle. The IR also provides output information during an unload or read/regenerate cycle. This register is composed of flip-flops, and if the IR partitioning option is employed, the portions, or zones, of the IR may be operated independently. The IR provides double-rail outputs to the external system.

## 3-3.6 Sense Amplifiers

The sense amplifiers receive the output of the selected cores through the sense lines, reject noise, and amplify the outputs to set the information register. The memory system has a separate sense amplifier for each bit of an information word. A sense winding common to all cores in a memory plane detects a change of state of an addressed core and provides an input signal to the associated sense amplifier. One bit of the selected word is applied to each sense amplifier, thus transferring the addressed word from storage to the IR, for further transfer to the external equipment.

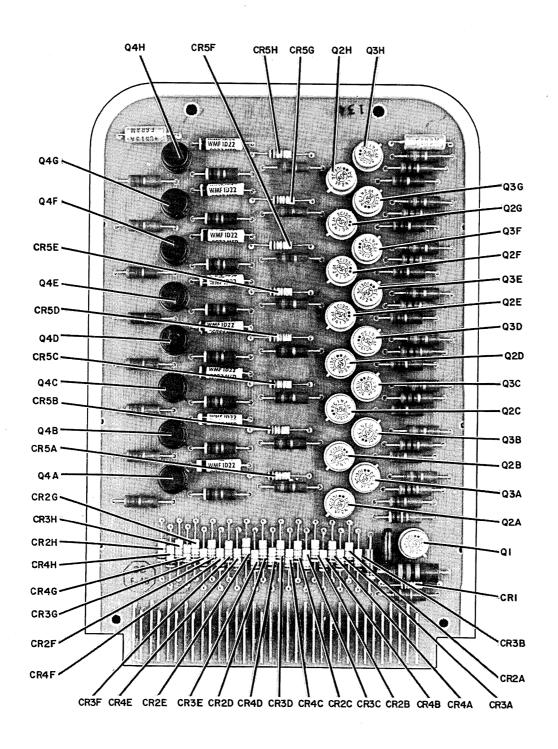

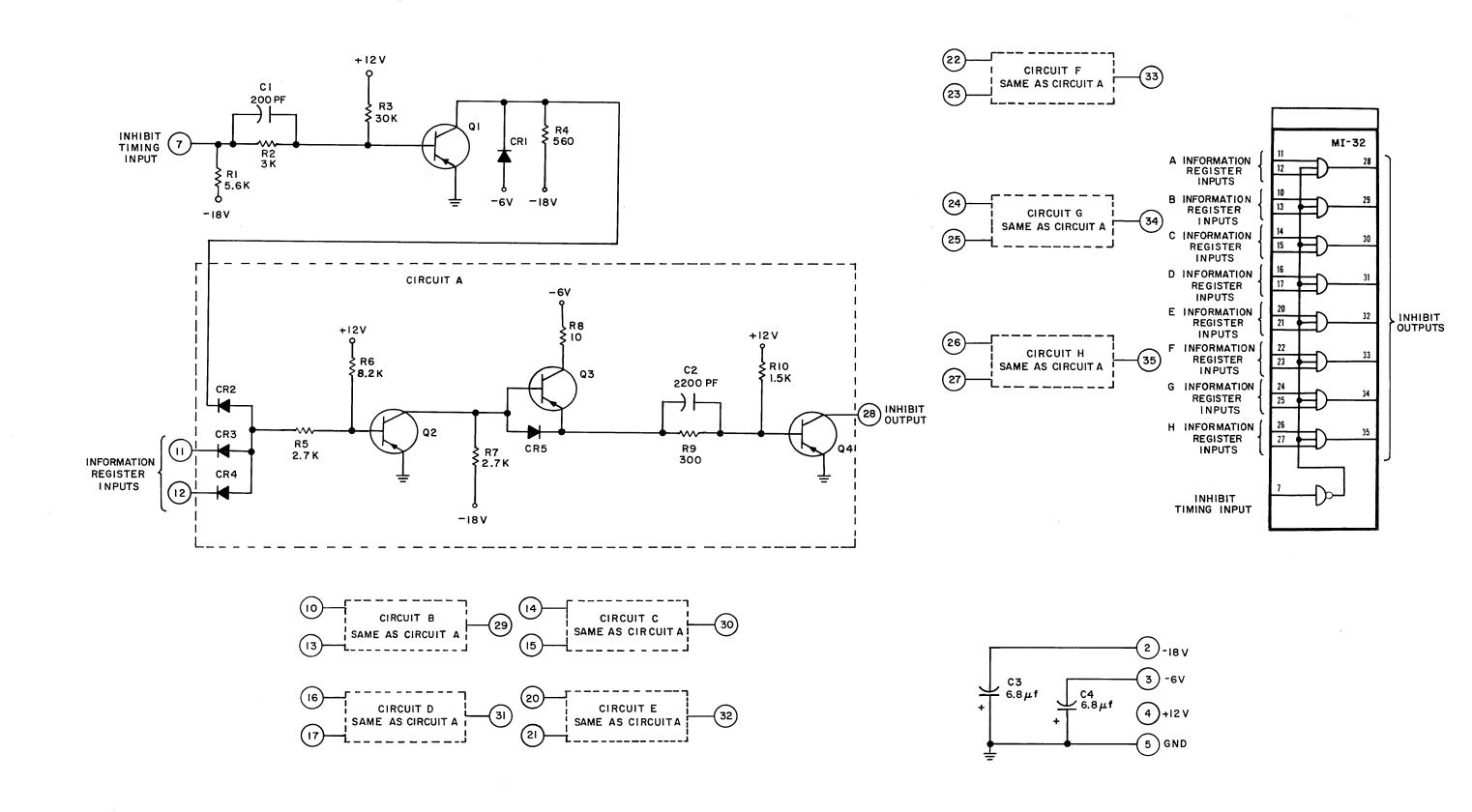

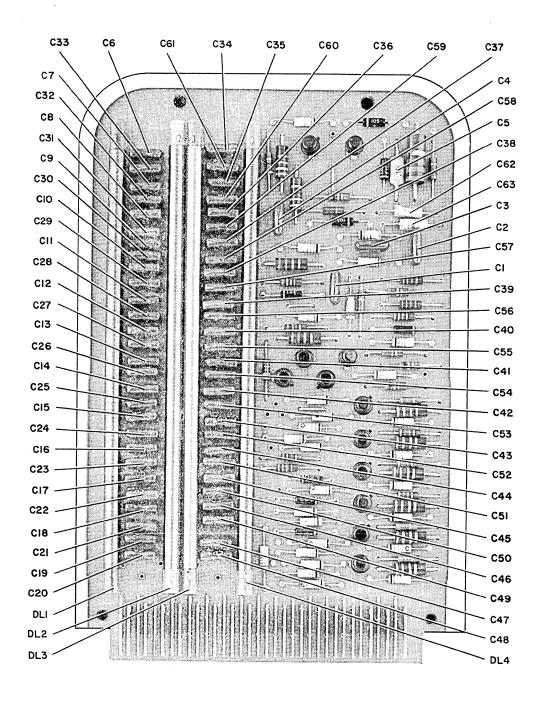

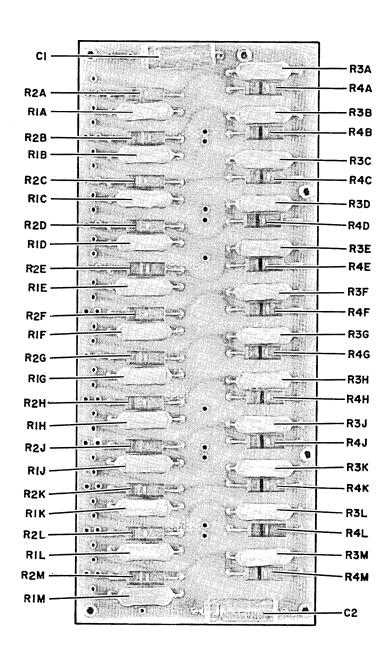

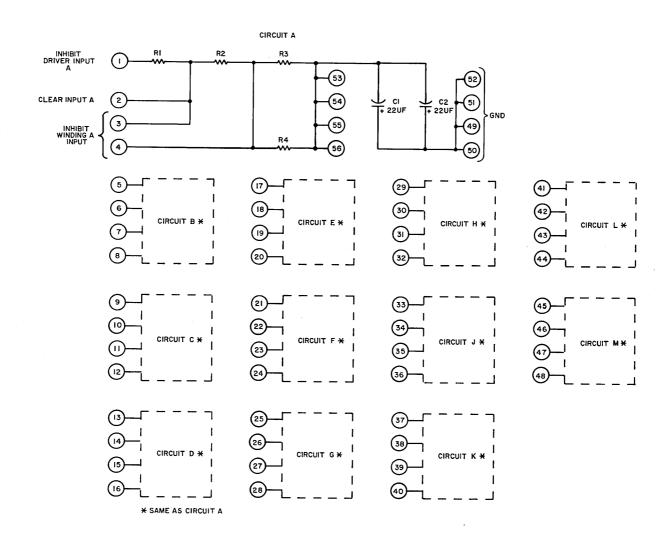

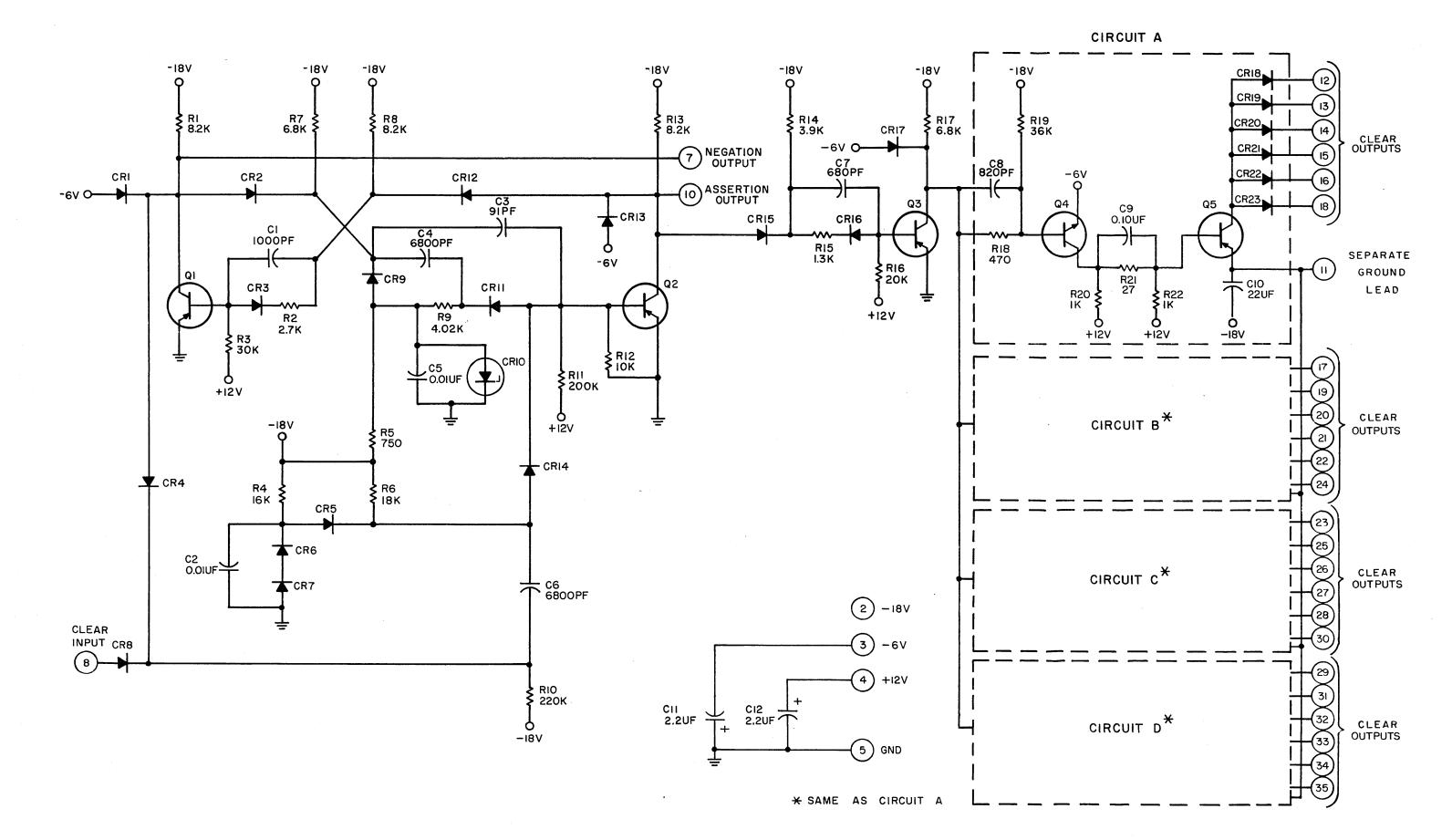

## 3-3.7 Inhibit Drivers

Each inhibit Driver PAC, Model MI-32, contains eight circuits and controls eight bits of a word. Each channel of an MI-32 PAC receives an input from the assertion output of one information register flip-flop. A timing signal (ZS or Z-step) is also received which is amplified to enable and properly time any channel. The MI-32 PAC is described in the PAC appendix. Each inhibit driver controls the flow of inhibit current through one plane of the memory core stack. Inhibit-driver conduction produces a half-select current when a ZERO is to be stored during load, clear/write or read/regenerate memory operations. An IR flip-flop disables its associated inhibit driver when a ONE is to be stored.

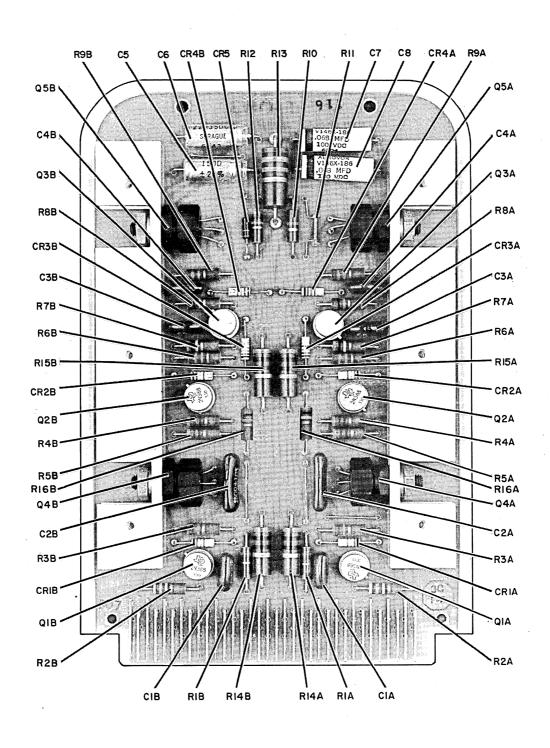

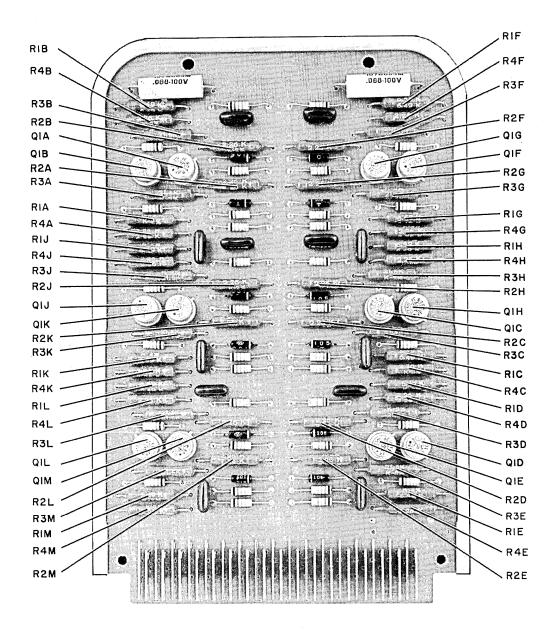

### 3-3.8 Current Drivers

The two Current Driver PACs, Model MD-32 are used in each TCM-32. A channel receives input signals from the  $\overline{\text{RS}}$  or  $\overline{\text{WS}}$  (read step or write step) gate and provides a selection current of proper rise-time, fall-time, and amplitude to a selected line. The MD-32 is described in the PAC appendix. Potentiometers for setting the output current amplitude are located adjacent to the core stack enclosure in unit 2.

# 3-4 FUNCTIONAL DESCRIPTION OF SELECTION AND DRIVING TECHNIQUE

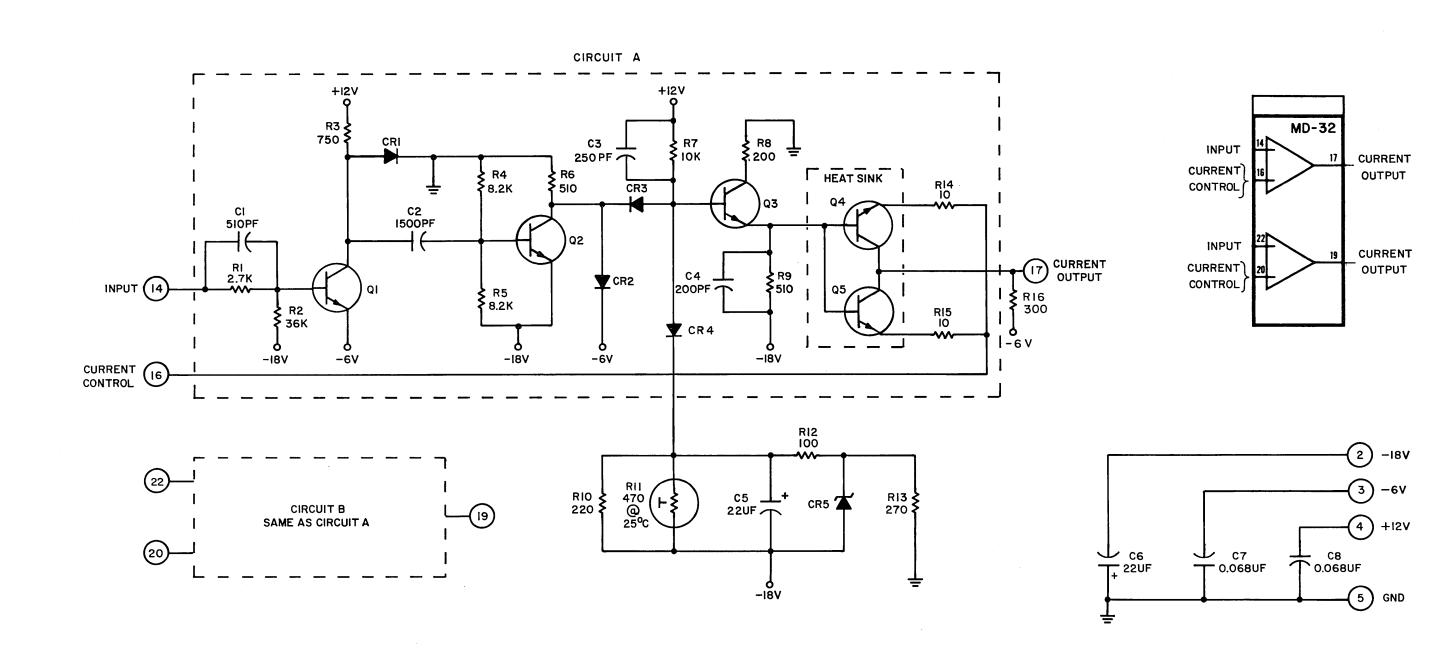

## 3-4.1 Memory Core Stack

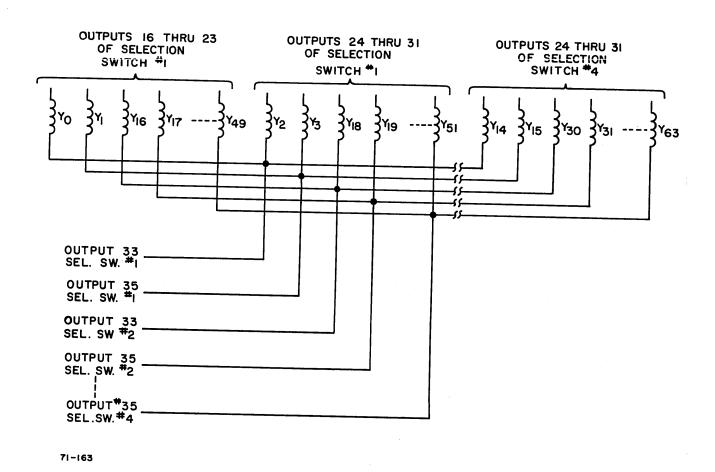

A typical schematic diagram of the memory core stack used in the memory system is illustrated in Figure 3-5. The ends of one side of the Y drive lines are connected in groups. Each group connects to a transistor switch on a Selection Switch PAC. The other side of the Y drive lines connect to outputs 16 through 31 of a Selection Switch PAC. The decoded input address information selects a transistor switch on each side of the Y drive lines. The logic design of the selection switches is such that only one line is selected for any input address. The X drive line connections are similar to the Y drive line connections.

Figure 3-5. Memory Core Stack, Simplified Schematic Diagram of Y-Coordinate Sense, and Inhibit

Inhibit driver outputs are applied to the corresponding inhibit lines designated  $Z_k$ . Resistors located on separate component boards control inhibit current amplitude and provide transient damping. (Information on the component board is included in the appendix.) The inhibit lines control the insertion of data into the memory core stack for storage

The sense lines control the extraction of data from storage within the memory core unit. A sense winding threads every core in a plane to minimize output signals due to inductive or capacitive coupling to other windings and those due to certain nonideal electrical characteristics of the magnetic cores.

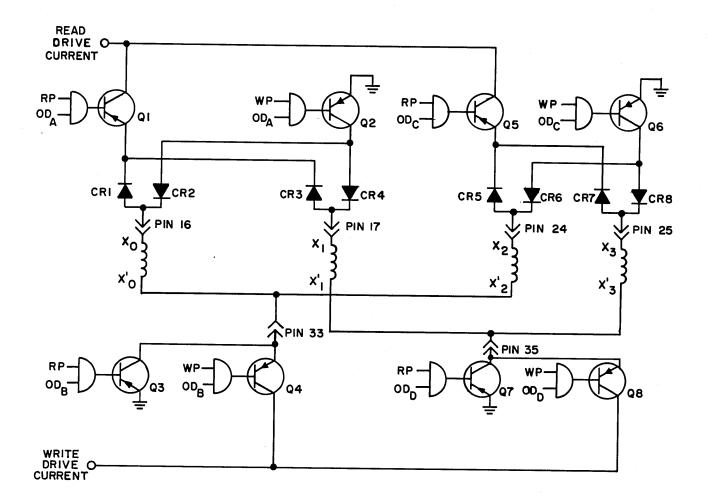

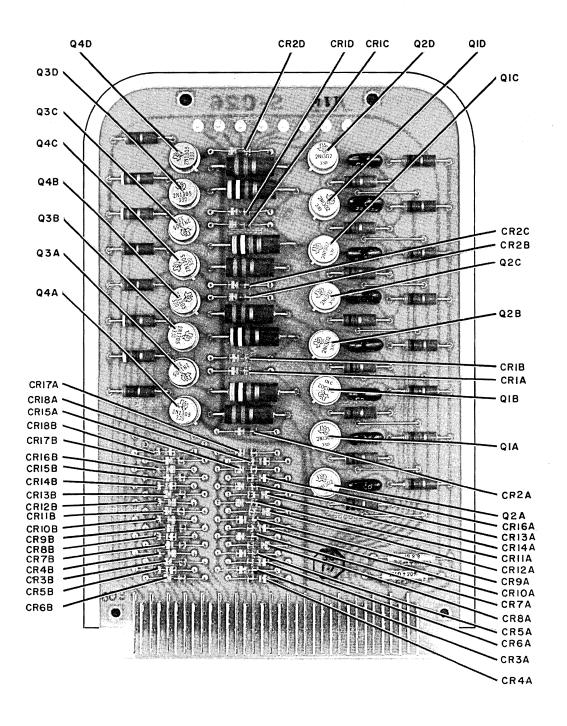

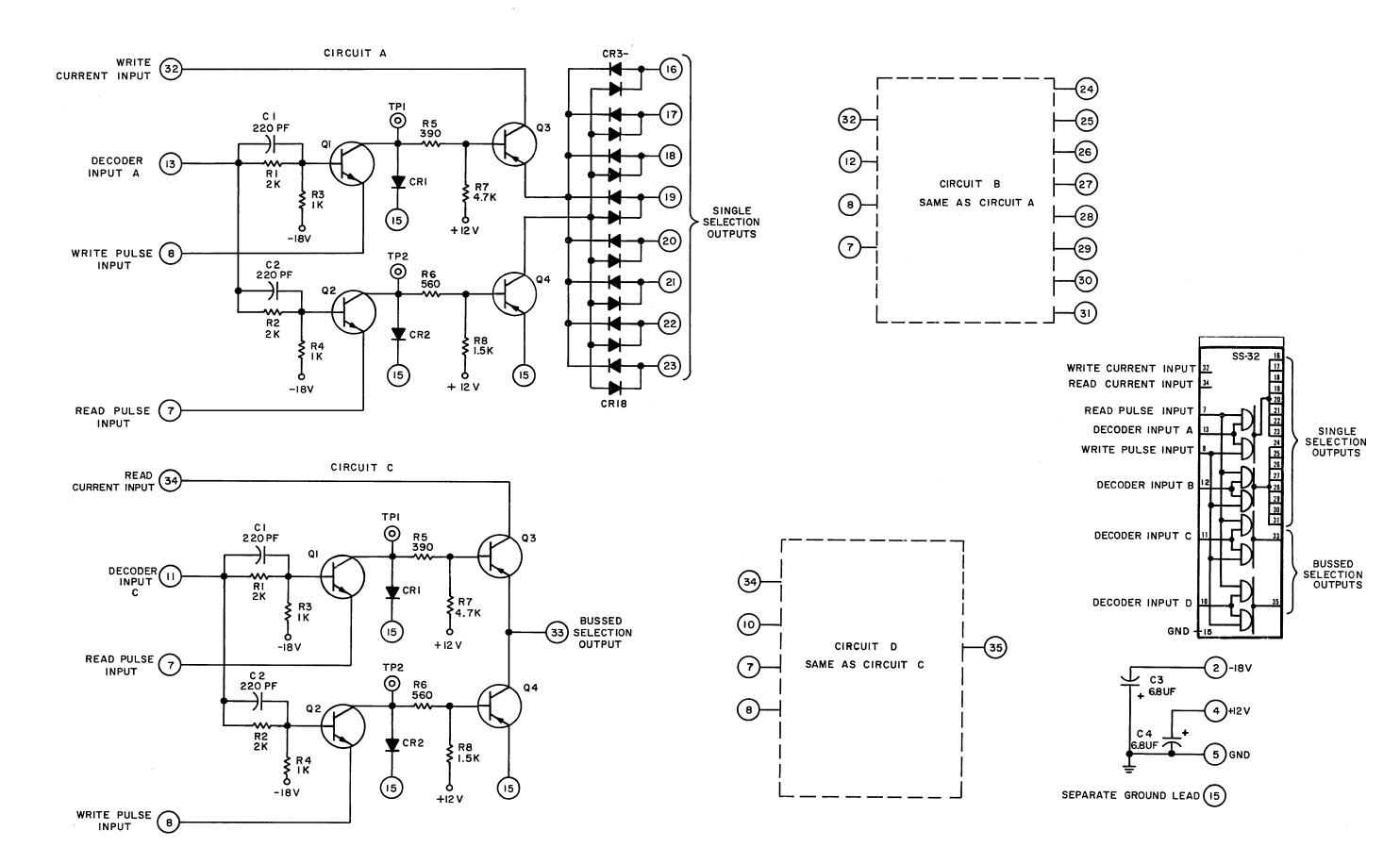

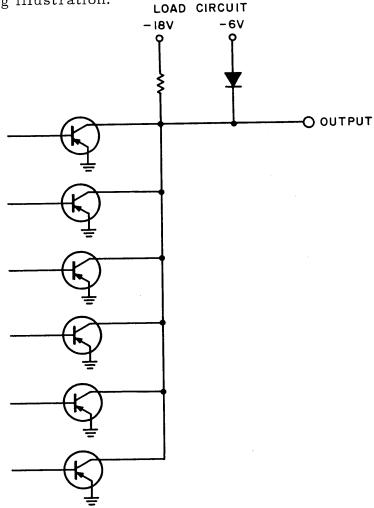

### 3-4.2 Selection Switches

The X-row selection and Y-column selection are composed of Selection Switch PACs. Relevant sets of digits of the address register are decoded and applied to the Y-column selection switches. Similarly, other sets of digits are decoded and applied to the X-row selection switches. Since only one X drive line and one Y drive line are selected for a given address register content, only one address receives the full coincident-current.

The method of selecting only one X drive line (or similarly one Y drive line) is demonstrated by the simplified selection diagram (Figure 3-6). To select drive line  $X_O$ , switches Ql and Q3 are turned on by coincidence of decoded address information (ODA and ODB) and the read pulse (RP). The other six switches are off. Read current flows from ground through Q3, memory line  $X_O$ , CRl and Ql to the read current source. The diodes are needed to steer the current through only the selected line. For instance, the current can not flow through the path Q3-X2-CR6-CR8-X3-X1-CR3 and Ql because of the reversed biased diode CR6.

During the write portion of the cycle, Q2 and Q4 are turned on by coincidence of the write pulse (WP) and ODA and ODB, respectively. Switches Q1 and Q3 are off due to the absence of a read pulse, and Q5, Q6, Q7, and Q8 are off due to the absence of an OD pulse. The write current flows from ground through Q2, CR2,  $X_0$  and Q4 to the write current source. The actual method used by the memory system to select the memory lines is explained as follows.

Figure 3-6. Simplified Selection Diagram

Figure 3-7. Internal Timing

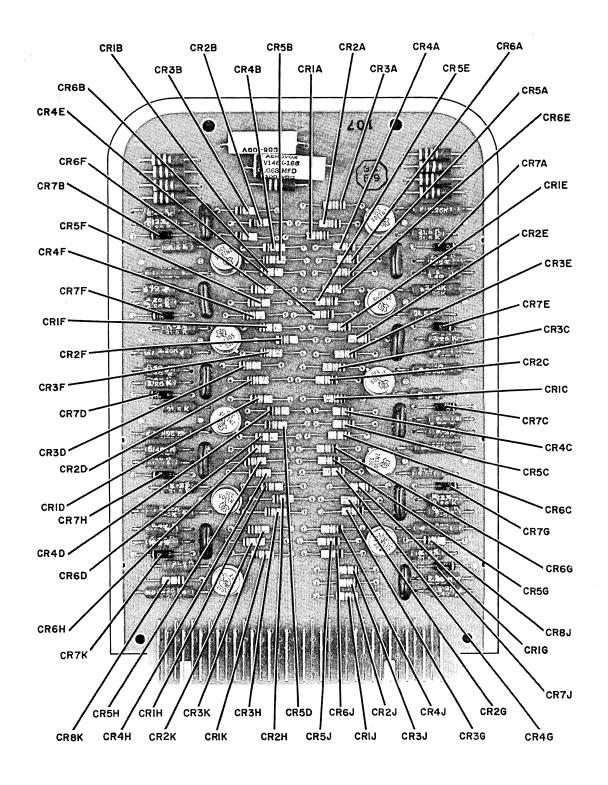

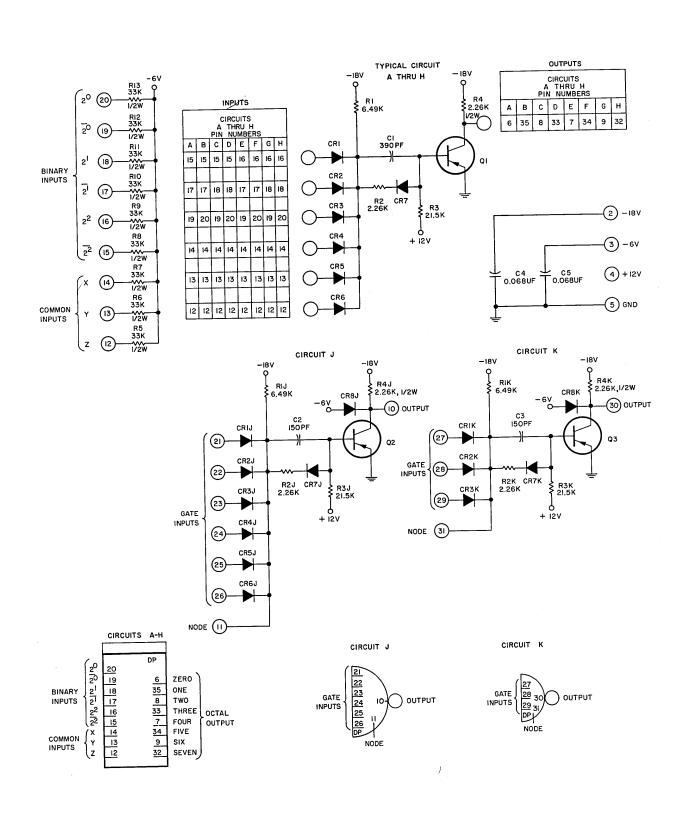

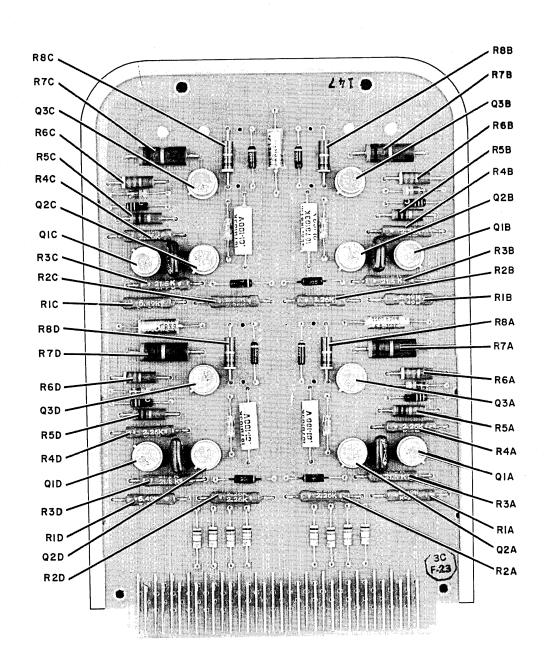

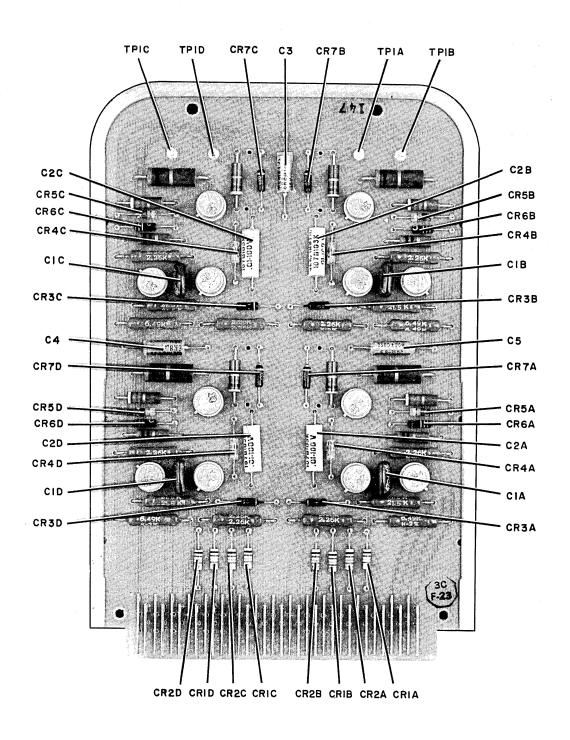

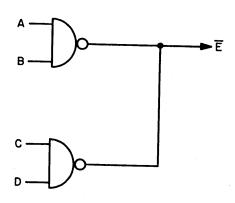

Contents of the address register are decoded in groups; that is, groups of three bits may be decoded into one of eight outputs via DP-32 (S-117).

Enabled outputs of the decoders go to particular inputs of Selection Switch PAC, SS-32, in which they are in turn gated against a read pulse or write pulse input to enable driver current flow of one polarity or the other through the selected coordinate lines.

## 3-4.3 Indicator Option

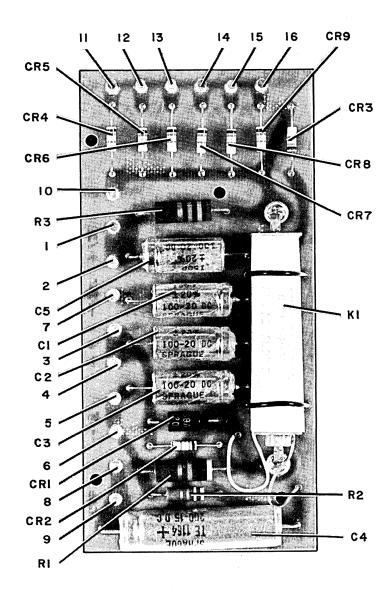

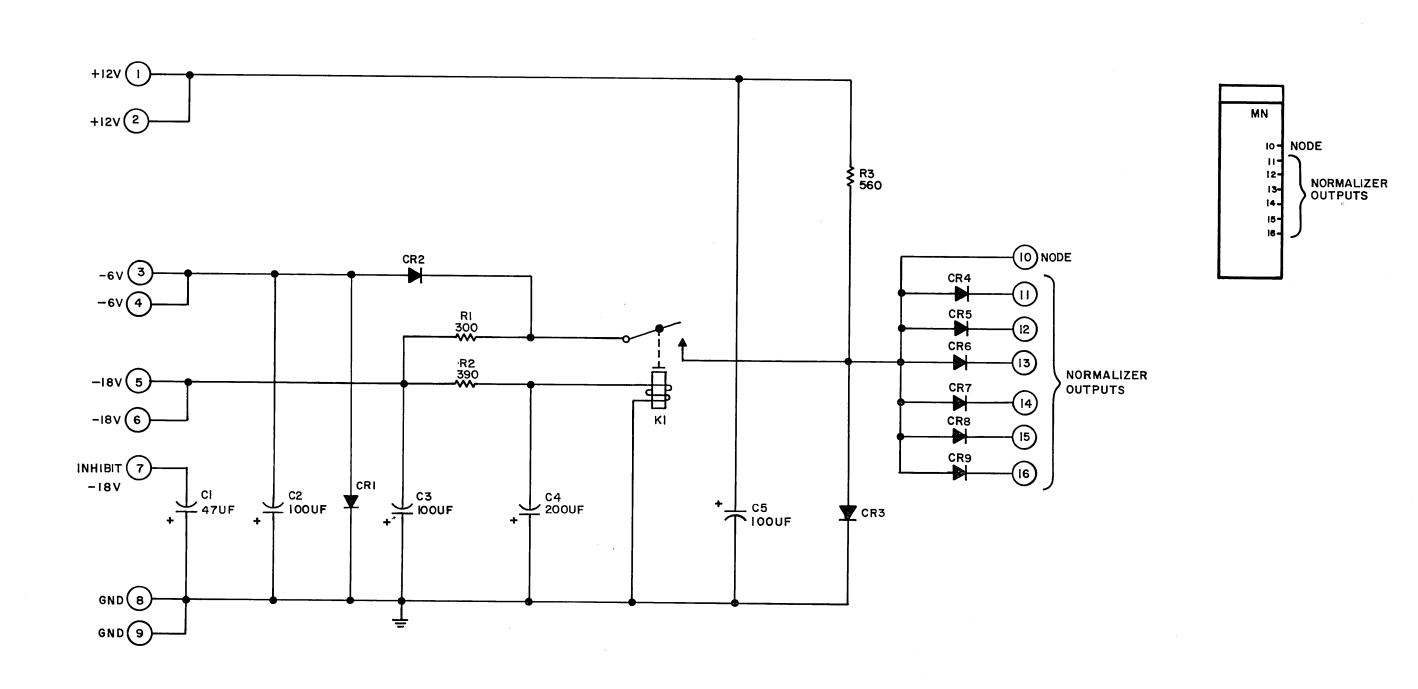

When used, the indicator option includes incandescent indicators on the front panel, associated LD-30 Driver PACs, and the Indicator Power Supply, Model PI.

### 3-5 OPERATING CYCLES

### 3-5.1 Standard Cycles

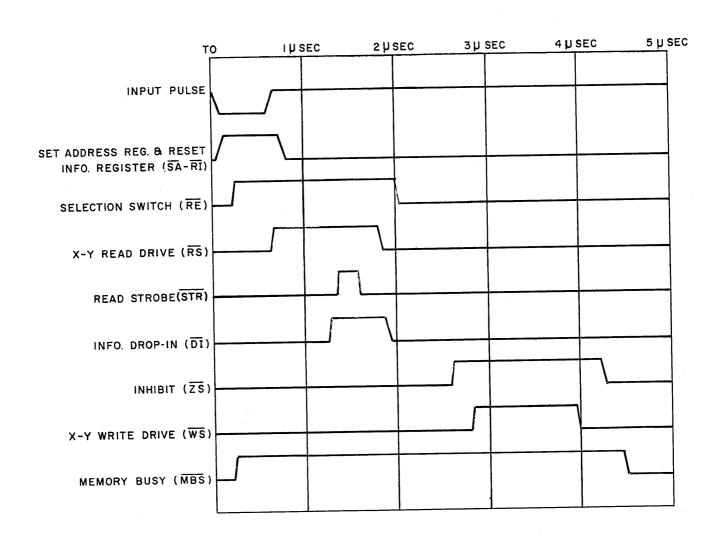

The four standard operating cycles of the TCM-32 Magnetic Core Memory are load, unload, clear/write and read/regenerate. The operating cycle or mode is selected by separate control pulses which are generated by the computer or external system. The control circuits are shown in the memory block diagram of Figure 3-4. The internal timing signals are shown in Figure 3-7, and the various internal logic signals are identified in Table 3-1.

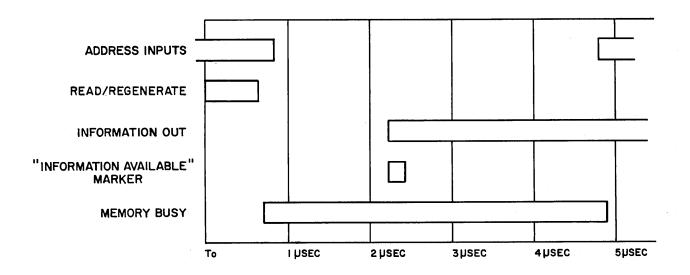

3-5.1.1 Read/Regenerate Cycle (Figure 3-8). - The read/regenerate cycle transfers a selected word from storage to the information register upon command. As the reading process requires the resetting of all selected cores to ZERO (destructive readout) the information in the information register is reinserted into core storage to avoid loss of the information. The information is also retained in the information register for use by the external system. A read/regenerate command is required for each word unloaded.

The read/regenerate sequence is as follows.

l. A core storage location corresponding to the word in the address register is selected.

Figure 3-8. Read/Regenerate Cycle External Timing

- 2. Information stored in the selected core storage location is read out into the information register, from which it is available to the external system. The information is also held in the information register.

- 3. The information in the information register is regenerated into core storage at the selected address.

The internal timing of the read/regenerate cycle is generated by two TD-32 PACs in the timing and control section of the memory (positions 22 and 23 of Unit 1). The first TD-32 generates the proper timing signals for the read half of the cycle; the second TD-32 generates the outputs and internal timing signals required for the regenerate portion.

Upon the initiation of a read/regenerate pulse, two timing pulses are generated by the TD, set address (SA), and reset information register  $(\overline{RI})$ . These pulses set up the new address in the address register and clear the information register to all ZEROs. Pulse RE next enables the selection switches to direct read the drive currents to the proper address. After the selection switches are enabled, the X and Y drive currents are turned on and timed by  $\overline{RS}$ . The outputs from the bits of the selected word are amplified by the sense amplifier. The read strobe pulse  $(\overline{STR})$  forms a part of the

detection of a logical ONE. Pulse  $\overline{STR}$  follows the X-Y drive currents so that it occurs at the exact time when the core turnover of a ONE being read out is at its peak. The outputs from the read amplifier are directed to the information register which is then set up according to the information read from the memory stack. The outputs of the information register supply the word to the external system.

The regenerate portion of the read/regenerate cycle is started by the inhibit drive pulse (ZS) which turns on the inhibit drivers. The width of this pulse brackets the X-Y drive pulse ( $\overline{WS}$ ) and, together with  $\overline{WS}$ , will restore the information word into the selected storage location. The end of ZS signifies the end of the read/regenerate cycle.

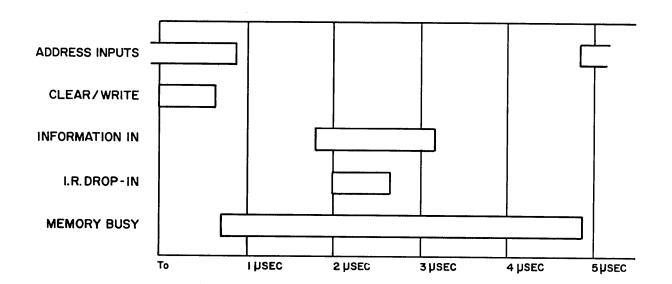

3-5.1.2 Clear/Write Cycle (Figure 3-9). - The clear/write cycle sets all the storage cores of the selected address to ZERO, thenloads the cores with an information word. A separate clear/write command is required for each word loaded and information is not read out when the cores are cleared.

Figure 3-9. Clear/Write Cycle External Timing

The clear/write cycle is made up of the following steps.

- 1. The core storage location corresponding to the word in the address register is selected.

- 2. The selected location is cleared of all previously stored information.

- 3. New information from the external system or computer is loaded into the information register.

- 4. The information in the information register is then written into the cleared storage location.

The clear/write cycle is initiated by an input pulse on the clear/write line. This cycle follows the same timing as does the read/regenerate cycle with one exception: a DI (information drop-in) signal will be generated to transfer the information into the information registers, and the read strobe (STR) pulse will not be present. The functional differences between the clear/write cycle and the read/regenerate cycle are as follows. The former will select a location, clear the information from that location, and write in the new information generated by the external system. The read/regenerate operation, on the other hand, will select a location, read the information from this location into the information register from which it can be sampled, and then restore the identical information back into the selected location in storage.

3-5.1.3 Load Cycle (Figure 3-10). - In the load cycle one information word is transferred from the information register to the storage cores at a selected address in response to a load command. The number of words stored is limited only by the word capacity of the core storage, but a separate load command is required for each word. Unless one of the optional methods of sequencing the address register is used, an externally generated address is required for each load command.

A load cycle consists of the following steps.

1. A core storage location is selected which corresponds to the address word held in the address register.

Figure 3-10. Load Cycle External Timing

- 2. An information word from the external system is loaded into the information register.

- 3. The information word in the information register is written into the selected core storage location.

The load cycle is identical to the second half of a read/regenerate or clear/write operating cycle. Upon the application of an externally generated load pulse, the second TD-32 PAC in the timing chain is activated. The load cycle has no provision for clearing the location to be written into. Therefore, this location must have been cleared (reset to ZERO) at the start of the load cycle.

3-5.1.4 Unload Cycle (Figure 3-11). - The unload cycle transfers one information word from core storage into the information register upon command. An externally generated address is required for each unload command unless the memory system is equipped with an optional method of automatically sequencing the address.

Figure 3-11. Unload Cycle External Timing

The unload cycle is identical to the first half of the read/regenerate or clear/write cycle. It is initiated by an external pulse applied to the unload command line. This pulse triggers the first TD-32 PAC in the timing chain. The timing chain produces the same timed sequences which are described in the read portion of the read/regenerate cycle. The second TD-32 is prevented from being triggered by the "not half cycle" signal (HC). The HC signal is generated by the output of a flip-flop, which is controlled by the unload input command. Because the unload cycle results in a destructive readout, it will leave the addressed location in a cleared or "reset to ZERO" state.

# TABLE 3-1. INTERNAL LOGIC SIGNALS

NOTE

Positive-going (-6 volts to 0 volt) signals are indicated by a bar over the signal designations.

| Designation   | Identification                                   |

|---------------|--------------------------------------------------|

| CW            | Clear/write command                              |

| RR            | Read/regenerate command                          |

| LB            | Load command                                     |

| UB            | Unload command                                   |

| SA            | Set address register                             |

| RI            | Reset information register                       |

| RE            | Enable read selection switches                   |

| RS            | X-Y read drivers                                 |

| STR           | Read strobe                                      |

| DI            | Information drop-in                              |

| ZS            | Inhibit step and enable write selection switches |

| <del>WS</del> | X-Y write drivers                                |

| MBS           | Memory busy signal                               |

| RMW           | Read/modify/write                                |

| RDM           | Random access input                              |

| LBA           | Load set address                                 |

| UCT           | Unload address count pulse                       |

| LCT           | Load address count pulse                         |

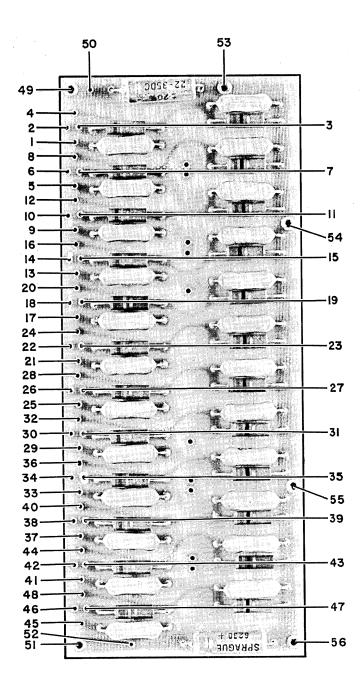

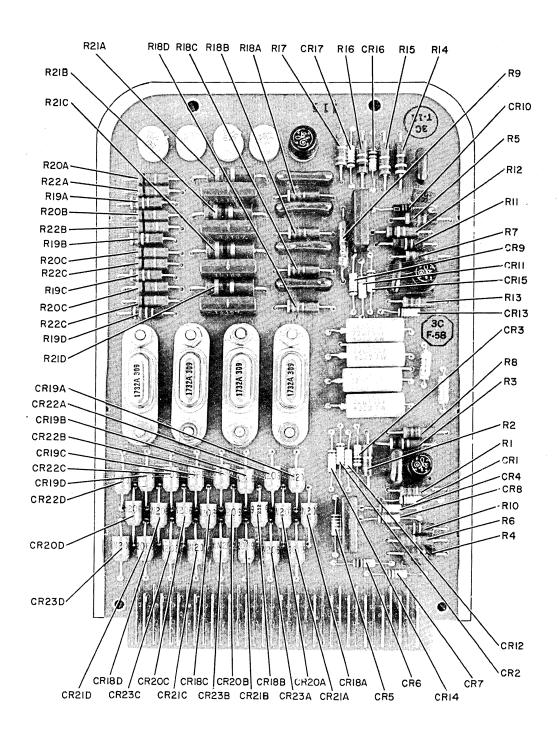

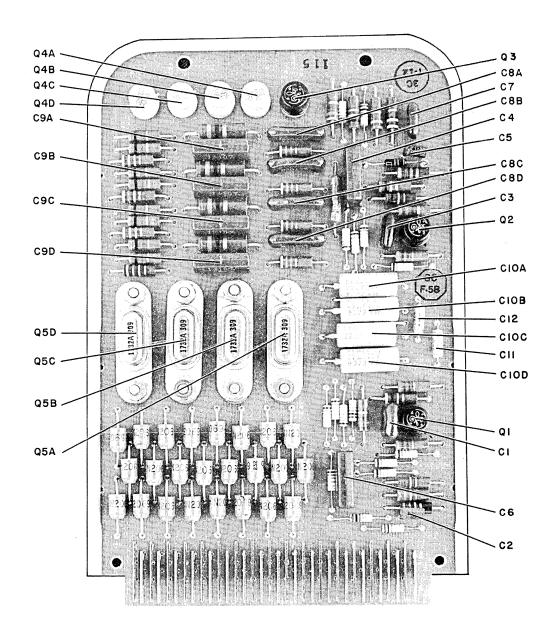

| RU            | Reset unload counter                             |